竞争与险象的讨论前提

当多个输入发生变化时,由于变化时刻以及延迟的影响,组合逻辑的输出中必然存在着不稳定态。但是通过上篇博文的分析:组合逻辑中的竞争与险象问题(一),我们发现即使仅有一个输入发生变化时,组合逻辑的输出仍可能存在问题,这便是组合逻辑中存在的最大隐患:竞争与险象。

什么是竞争?

组合逻辑的本质是与或非门,因此无论多么复杂的电路,其本质都是上面三种运算组成。由于竞争是针对仅有一个输入变化的组合逻辑而言的,而任意一个组合逻辑的输入电信号,都是经历若干个与或非门后才到达输出端的,因此为了搞清楚竞争,有必要对这些基本逻辑运算进行分析:

注:下面提到的开关,开代表接通状态,关闭代表断开状态。

(1) 门电路的开关特性

非门可以看做一个常开的开关,因此任意一个输入到非门的信号都会被取反输出。

与门具有开关特性,因为它至少由两个输入端,假设有L个输入端,那么如果L-1个输入端置1,那么对于剩下的一个输入端而言,该与门就相当于一个打开的开关,输出取决于最后一个输入端上的值。

如果其中一个输入端为0,那么对于其他L-1个输入端而言,该与门就相当于一个关闭的开关,无论其他输入端是什么,输出总是0.

或门具有开关特性。假设一个L个输入端的或门,如果任意一个输入端为1,则对于其他L-1输入端而言,该或门相当于一个关闭的开关,因为无论其他输入端为什么,输出总位逻辑1;如果L-1输入端为逻辑0,那么对于最后一个输入而言,该或门相当于一个常开的开关,输出值取决于最后一个输入。

(2)门电路的半开关特性

非门不具有半开关特性,因为只有一个输入端。

与门具有半开关特性:当且仅当与门中有两个或以上的输入端都是由组合逻辑中的一个输入电信号直接或间接驱动时,称该与门具有半开关性,因为此时,与门的其他输入端(如果有)对该与门仍具有开关性。因此,对于一个具有半开关性的N输入与门来说,它可以等效为一个M(M小于等于N)输入与门和开关的级联。

或门同样如此,略。

半开关是多进一出的情况,正是导致电路出现问题的隐患所在。

(3)竞争的定义

如果在某一个时刻,从组合逻辑的某一个输入端到其输出端存在两条以上的电信号通路时,就称该组合逻辑在当前状态下针对这个输入端存在竞争。

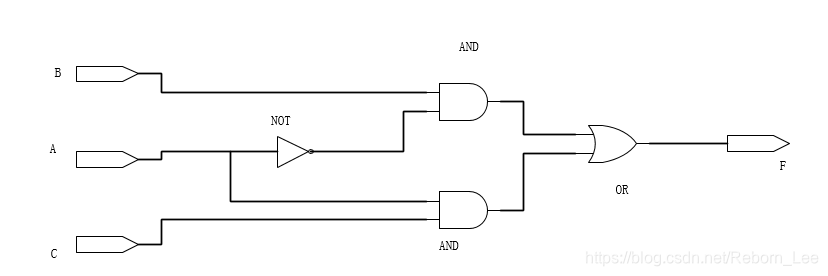

对于下图:

该电路的或门就是一个半开关,那么就可能存在竞争,那什么时候存在竞争呢?且看下面的分析:

当 B = 1,C = 1时,对上图进行化简:

输入端A存在竞争。

当B = 0,C= 1时,如下:

可见,电路中没有半开关,不存在竞争。

当B,C都等于0时,化简后的电路输出恒为零,不存在竞争。