基于的平台是Vivado 2018.2

本文主要以一个简单的半加器加器(组合逻辑为例)学习vivado的综合,I/O配置的一些内容。

本人小白,记一些自己的理解。

任务:

- 分析Log文件。

- 布局I/O管脚

- 分析两个视图

- 分析约束.xdc文件

首先介绍半加器:

链接地址:http://www.elecfans.com/dianzichangshi/20170816539743.html

我们尽关注半加器的逻辑结构:

假设输入端子为A,B

输出端子为S

进位端子为C

则我们有 S = A xor B;C = A & B;

那么我们去写我们的verilog代码(vivado的使用会再今后进行简单说明。我们假设已经会了怎么新建工程。)

半加器代码如下:

module half_add(

input A,

input B,

output S,

output C

);

assign S = A ^ B;

assign C = A & B;

endmodule

我们按照这张真值表编写testbench文件:

`timescale 1ns / 1ps

module half_sim();

reg data_1;

reg data_2;

wire S;

wire C;

half_add test(

.A(data_1),

.B(data_2),

.S(S),

.C(C)

);

initial begin

#200;

data_1 = 1'b0;

data_2 = 1'b0;

#200;

data_1 = 1'b0;

data_2 = 1'b1;

#200;

data_1 = 1'b1;

data_2 = 1'b0;

#200;

data_1 = 1'b1;

data_2 = 1'b1;

#200;

$finish;

end

endmodule

运行仿真结果如下:

显然这和我们的真值表是对应的。

以上部分属于基本操作,下面我们正式进入我们的任务:

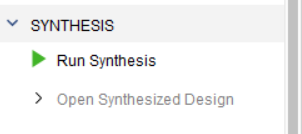

- 分析综合后的Log文件:

- 首先我们run synthesis

- 综合结束后我们取消,先不进行下一步实现。

- Xilinx官方推荐我们在综合后,实现前进行IO布置和时钟约束。

- 下面我们来看生成的Log文件都写了些什么。

- 我们在① 的位置看到了我们的license文件的使用,当我们需要实现综合操作时,首先软件会检查我们是否获取了license。

- 从②我们可以看到,此时我们还没有添加约束文件(先不要管约束文件是干嘛的,这个约束文件就是.xdc文件)

-

-

- 从3可以看到,我们的是两输入,一个异或逻辑。

- 从3.1看到我们有(的DSP和BRAM资源的个数),这个并不是我们使用的个数。

- Block RAM是PL部分的存储器阵列,为了与DRAM(分布式RAM)区分开,所以叫块RAM。ZYNQ的每一个BRAM 36KB,7020的BRAM有140个(4.9M),7030有265个(9.3M),7045有545个(19.2M)。每一个BRAM都有两个共享数据的独立端口,当然是可以配置的,可用于片内数据缓存、FIFO缓冲。

- 原文:https://blog.csdn.net/u014485485/article/details/78882027

- 常见资源介绍

- :http://www.elecfans.com/dianzichangshi/20170517517040.html

- 从④我们可以看到,该模块使用了2个LUT,2个输入缓冲区(Input-Buff)A一个,B一个,和两个输出缓冲区(Output-Buff)S一个,C一个。

-

-

-

- 从5我们看到未使用black box。

- 通俗点讲LUT就是像函数一样,对应关系就是逻辑表达式,给你输入,你可以查询到一个输出。举个例子里说:如何用4输入LUT实现表达式X。就是推测EEPROM中的值,你可以画出X的对应真值表,应该不难。如图所示:

- 如果A=1,B=1,C=0,D=0那么X=1,以此类推,A,B,C,D控制门控开关,让其选通相应的函数值到X端。

- https://www.cnblogs.com/Dinging006/p/9512506.html

-

以上就完成了任务一的分析。

- 我们开始布局I/O

- 对I/O进行简单说明

- MRCC/SRCC:时钟

- User I/O:同样IO

- 被占用的 User I/O

- 电源(红色):VCCINT VCCBRAM VCCAUX VCCAUX_IO

- Config(与做配置相关的管脚)

- 我们进入约束界面(点击红色线)

- 会提示我们没有约束文件,是否要创建约束文件,我们取消。

- 进行I/O配置

- 通过①进入Package视图

- ②进行选中我们要进行布置的管脚

- 3是管脚对应的电平状态

- 常见电平标准:https://wenku.baidu.com/view/10365452f01dc281e53af0f6.html

- 我们放置在了这几个位置

- 放大后可以看到

- 我们以B为例,进行具体分析

-

-

- 接着在DEVICE视图下我们可以看到我们刚才设置的管脚的位置。

- 红色圈住的地方就是我们的I/O管脚

例如我们的S管脚。

例如我们的S管脚。

-

下面我们implement 并观察生成的.xdc文件

set_property :设置属性

PROHIBIT :禁止使用(true表示确认禁止使用)

[get_sites B13]:寻找到B13文件。

set_property PROHIBIT true [get_sites B13]

set_property PROHIBIT true [get_sites B3]

set_property PROHIBIT true [get_sites D10]

set_property PROHIBIT true [get_sites D12]

set_property PROHIBIT true [get_sites D2]

set_property PROHIBIT true [get_sites E4]

set_property PROHIBIT true [get_sites F1]

set_property PROHIBIT true [get_sites F11]

set_property PROHIBIT true [get_sites G11]

set_property PROHIBIT true [get_sites G8]

set_property PROHIBIT true [get_sites H7]

set_property PROHIBIT true [get_sites J12]

set_property PROHIBIT true [get_sites J2]

set_property PROHIBIT true [get_sites K4]

set_property PROHIBIT true [get_sites L1]

set_property PROHIBIT true [get_sites L5]

set_property PROHIBIT true [get_sites M13]

set_property PROHIBIT true [get_sites M3]

set_property PROHIBIT true [get_sites N10]

set_property PROHIBIT true [get_sites P5]

set_property IOSTANDARD LVCMOS18 [get_ports C]

set_property IOSTANDARD LVCMOS18 [get_ports B]

set_property IOSTANDARD LVCMOS18 [get_ports S]

set_property PACKAGE_PIN A2 [get_ports A]

set_property PACKAGE_PIN A3 [get_ports B]

set_property PACKAGE_PIN A4 [get_ports C]

set_property PACKAGE_PIN A5 [get_ports S]

set_property IOSTANDARD LVCMOS18 [get_ports A]

我们进行implement操作之后就可以看见电路中的实现

左图我们看到两个LUT2实际上是同一个。

这个坑的内容以后会慢慢完善。