版权声明:本文为博主原创文章,转载需注明出处。 https://blog.csdn.net/zz_Caleb/article/details/84582021

常用命令:

Set_input_delay,create_clock,set_output_delay以及用于组合逻辑的set_max_delay.

Input delay:

- 什么是输入延时?

- Trace delay(又叫做board delay)板级延时

- 输入延时:以上游芯片的发送沿(launch edge)为参考点。发送数据之后,经过input delay这么长时间。数据到达fpga的输入端口的管脚。

- 以上游芯片的发送沿为参考点,经过四纳秒,数据到达fpga的输入端口。

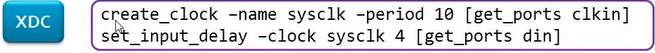

- 完整的例子

- FDRE:第一集触发器(first D register)

- Input setup timing report summary

- Input Hold timing report

- Summary

- 详细时许报告

- Summary

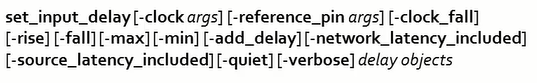

- Set_input_delay基本语法规则

- –clock:设置参考时钟,通常认为是上升沿为参考点

- –max

- –min

- Eg:

- DDR

- 系统同步:两片芯片共用时钟。

- Source synchronise:源同步

- DDR模式:上升沿发送的数据用下降沿来捕获,下降沿发送的数据用上升沿来捕获。

- –clock_fall(使用下降沿作为参考沿)

- –add_delay同时有效

- 静态时序路径

- 一定是从一个触发器到另一个触发器,不管这两个触发器是否在同一个芯片内,只有在这两个触发器之间才能构成一个完整路径。

- 在默认情况下,输入端口到达内部第一级触发器的路径并不是一个完整的时序路径。

- 要素

- 时钟,是外部芯片发送沿做为参考点

- 然后发送数据经过Tco再加上board delay到达fpga的输入端口。

- Summary

- Expr:计算求和