1、FPGA资源消耗分析

多PE并行系统的资源消耗包括占用基本单元数量和片上存储空间数量。FPGA中的PE是由基本单元组合实现某一功能的电路模块。Xilinx公司系列的FPGA中,基本单元由若干slices组成,因此,PE资源消耗可用占用的slices数量表示。基本单元主要包括:加法器、乘法器、比较器、移位寄存器。

对于多PE并行系统,假定单PE的资源消耗为一确定的常量,则随着PE数量的增加,系统运行时间会越来越短,而资源消耗则越来越大。运行时间的缩短伴随着资源消耗的增大,运行时间与资源消耗随PE数量变化呈相反的趋势。

2、Modelsim中wave窗口工具使用技巧

(1)Zoom Full,信号的所有周期变化在wave中显示

(2)统计前后时钟周期之差

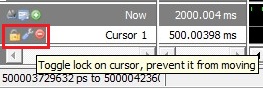

a.将黄色竖线移动到起始时钟处,点击左下角黄色小锁,锁定,黄色竖线变成红色竖线。

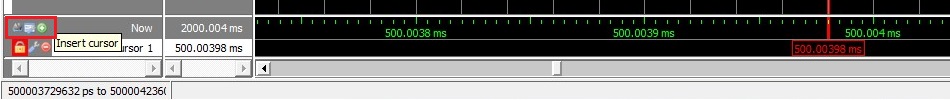

b.点击左下角绿色加号,再添加一条黄色竖线。此时,wave中存在一条黄线和一条红线。

扫描二维码关注公众号,回复:

5188881 查看本文章

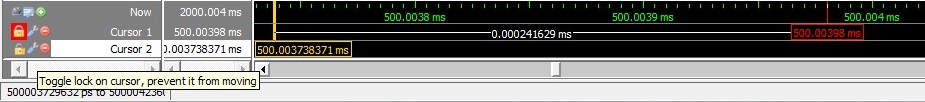

c.将新添加的黄线移动到终点时钟处,点击左下角黄色小锁,锁定。

如图所示,可以看到两条线之间的周期之差为500ms。

(3)修改wave上时间单位

a.在wave窗口的下方时间轴上右击,点击Grid & Timeline Properties。

b.在Time units中选择合适的时间单位。

3、FPGA主要有三种设计方式

a.原理图:通过在原理图内输入各种与门、非门、或门逻辑,进行连线,最终得到设计。当设计到较大系统时,设计非常复杂,所以不推荐。

b.Verilog HDL设计方式。

c.IP核输入方式。

一般设计时,会将Verilog HDL设计方式和IP核输入方式结合使用。