TCAM 三态内容地址查找存储器,CAM内容地址查找存储器。区别在于TCAM多了一级掩码功能,也就是说可以指定某几位是dont care。匹配的时候0,1都行的意思。

广泛应用于数据流处理领域,本文简要介绍TCAM和CAM的逻辑组成和Verilog实例。

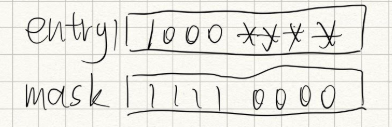

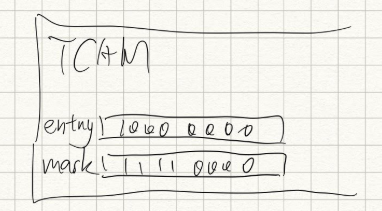

TCAM对于一个带mask的表项,如:“1000 * * * * ”。我们首先将其分解为entry1 和 mask:

令entry2 = entry & mask

所以entry2 = 10000000

我们将entry2 和mask 存入TCAM表项组中。

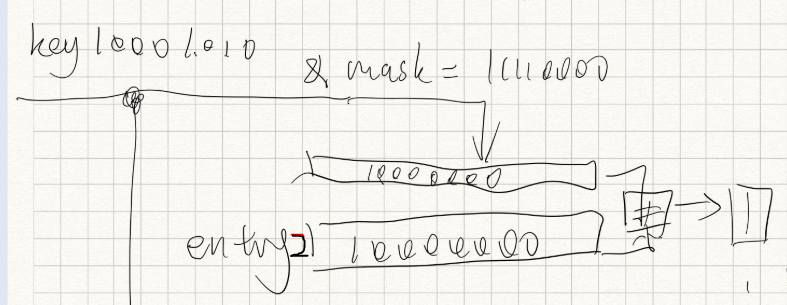

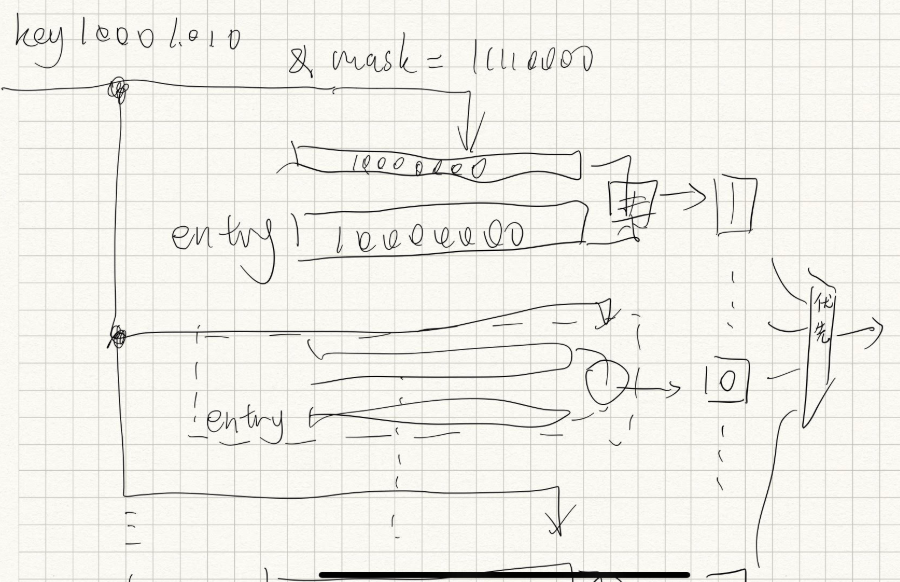

在做查找的时候,key广播到每个表项组中。之后将key和当前表项组中的mask做与运算,如key = 10001010. key& mask = 10001010 & 11110000 = 10000000

最后再和entry做比较,如果相等则将1写入结果寄存器。之后所有的结果汇总到优先级选路器中。并得到id编号。

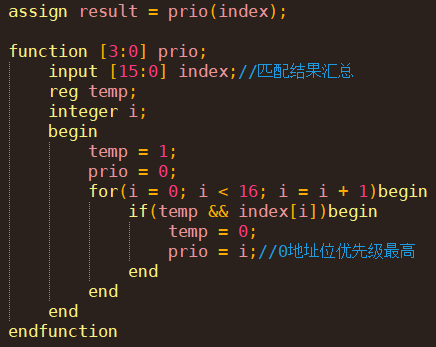

优先级选路器:

可以用function函数实现:

参考代码请看这里一个粗糙的实现:https://github.com/qiaosiyi/progASICp4SWITCH/blob/master/tcam.v

这样我们基本上就可以用Verilog语言去实现了,其次要注意的是,广播,复制,或者做逻辑运算,都会比较占用时延,不要在一个时钟周期去做,很可能无法完成时序约束。

建议一个操作使用一个时钟周期,所以tcam查找我这里延迟了四个周期,但是fully-pipeline。吞吐还是一周期一次。

有时候表项很多,也许优先级选路器timing收不了,其实可以考虑将这一步延长俩周期做。