SPartan6 FPGA中, PLL产生的时钟不能直接连到FPGA的通用I/O上;

如果硬件已经连上了,可通过在PLL输出与通用I/O之间增加ODDR2模块缓冲来解决。

ODDR2与PLL模块可放在一个V文件中。

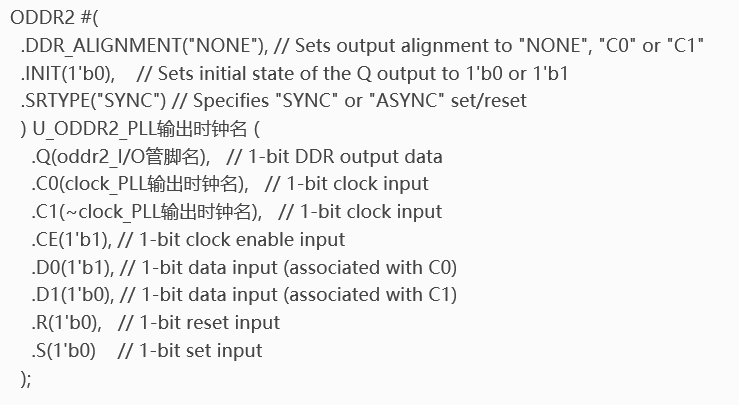

ODDR2模块如下:

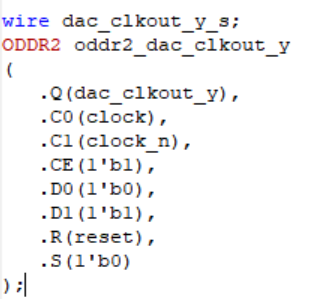

在实际应用中,用于驱动快慢轴运动,PLL后接的oddr2模块

oddr2_dac_clkout_y为模块名

Q为oddr2输出的引脚-dac_clkout_y

C0为oddr2输入的PLL时钟信号

C1为oddr2输入的PLL时钟信号的取反

CE、D0、D1、R、S按照模块要求设置即可