首先对于Cameralink的相关介绍转自下面的文档:

https://wenku.baidu.com/view/7470181779563c1ec5da71ec.html(Cameralink简介)

https://wenku.baidu.com/view/ff8a623181c758f5f71f673f.html(cameralink_v2.0中文版)

上面链接总结的很好,我在这里再转载一下

CameraLink是一种专门针对机器视觉应用领域的串行通信协议,使用低压差分信号LVDS传输。CameraLink标准在ChannelLink标准的基础上有多加了6对差分信号线,4对用于并行传输相机控制信号,其它2对用于相机和图像采集卡(或其它图像接受处理设备)之间的串行通信。CameraLink标准中,相机信号分为四种: 电源信号、视频数据信号(ChannelLink标准)、相机控制信号、串行通信信号、视频数据信号。

视频数据信号部分是CameraLink的核心,该部分为其实就是Channel Link协议。主要包括5对差分信号,即X0-X0+、X1-X1+、X2-X2+、X3-X3+、Xclk-~Xclk+;视频部分发送端将28位的数据信号和1个时钟信号,按7:1的比例将数据转换成5对差分信号,接收端使用Channel Link芯片(如Channel Link转TTL/CMOS的芯片DS90CR288A)将5对差分信号转换成28位的数据信号和1个时钟信号。 28位的数据信号包括4位视频控制信号和24位图像数据信号。

4位视频控制信号

FVAL:帧同步信号。当FVAL为高时表示相机正输出一帧有效数据

LVAL:行同步信号。当FVAL为高时,LVAL为高表示相机正输出一有效的行数据。行消隐期的长短由具体的相机和工作状态有关。

DVAL:数据有效信号。当FVAL为高并且LVAL为高时,DVAL为高表示相机正输出有效的数据,该信号可用可不用,也可以作为数据传输中的校验位。

CLOCK:这一信号为图像的像素时钟信号,在行有效期内像素时钟的上升沿图像数据稳定。值得说明的是,CLOCK信号单独采用一对LVDS信号传输,不管相机是否处于工作状态,CLOCK信号应该始终有效,它是ChannelLink芯片的输入时钟,是ChannelLink芯片之所以能在4对信号线中传输28位数据,就是因为对CLOCK信号7倍频的结果。

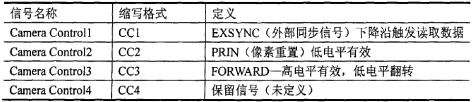

相机控制信号

CameraLink标准定义了4对LVDS线缆用来实现相机控制,它们被定义为相机的输入信号和图像采集卡的输出信号。一般情况是这些信号命名为:

CameraControl1(CC1)

CameraControl2(CC2)

CameraControl3(CC3)

CameraControl4(CC4)

串行通信信号

CameraLink标准定义了2对LVDS线缆用来实现相机与图像采集卡之间的异步串行通信控制。相机和图像采集卡至少应该支持9600的波特率。这两个串行信号是相机:

SerTFG(相机串行输出端至图像采集卡串行输入端)

SerTC(图像采集卡串行输出端至相机串行输入端)

其通信格式为:1位起始位、8位数据位、1位停止位、无奇偶校验位和握手位。

相机电源并不是由CameraLink连接器提供的,而是通过一个单独的连接器提供。

视频传输模式

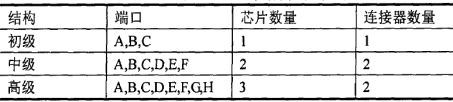

由于单个Camera Link芯片只有28位数据可用,有些相机为了提高传输数据的效率,需要几个Camera Link芯片。按使用要求不同,视频传输模式分为三种配置:Base(基本或初级)配置为一个Camera Link芯片,一根电缆; Medium(中档或中级)配置为两个Camera Link芯片,一根电缆; Full(全部或高级)配置为两个Camera Link芯片,两根电缆。

Base模式需要一块ChannelLink的芯片和一个CameraLink机械接口,发送器在每个像素时钟里发送 28bits数据,包括4bits的图像使能信号和24bits的图像数据。4bits图像使能信号包括:帧有效信号 (FVAL),高电平有效,它的反相即为帧同步信号;行有效信号(LVAL),高电平有效,它的反相即为行同步信号;数据有效信号(DVAL),只有在数据有效信号为高电平时,图像采集卡才接受图像信息。24bits图像数据可以是一个像素点的24-bitRGB数据、3个像素点的8-bit黑白图像数据、1到2个像素点的10-bit或12-bit的黑白图像数据、一个像素点的14-bit或16-bit的黑白图像数据。

Medium模式需要两块Channe1Link的芯片和两个CameraLink机械接口,发送器在每个像素时钟里发送4Obits数据,包括4bits的图像使能信号和36bits的图像数据。4bits图像使能信号与Base模式下相同。36bits图像数据可以是一个像素点的36-bit或30-bitRGB数据、4个像素点的8-bit黑白图像数据、3到4个像素点的10-bit或12-bit的黑白图像数据。

Full模式需要三块Channe1Link的芯片和两个CameraLink机械接口,发送器在每个像素时钟里发送68bits数据,包括4bits的图像使能信号和64bits的图像数据。4bits图像使能信号与Base模式下相同。

端口分配

对于Base模式,28位数据信号中包括三个数据端口:A口(8位)、B口(8位)、C口(8位);四个视频控制信号FVAL(帧有效)、DVAL(数据有效)、LVAL(行有效)、SPARE(空,暂时未用)。

在Base(初级)结构中,端口A,B和C被分配到唯一的Cameralink驱动器/接收器对上;在Medium(中级)结构中,端口A、B和C被分配到第一个驱动器接收器对上,端口D,E和F被分配到第二个驱动器/接收器对上;在FULL(高级)结构中,端口A、B和C被分配到第一个驱动器/接收器对上,端口D,E和F被分配到第二个驱动器/接收器对上,端口G和H被分配到第三个驱动器/接收器对上。

如果相机在每个周期内仅输出一个像素,那么就使用分配给像素A的端口;如果相机在每个周期内输出两个像素,那么使用分配给像素A和像素B的端口;如果在每个周期内仅输出三个像素,那么就使用分配给像素A,B和C的端口;依此类推至相机每周期输出八个像素,那么分配给A到H的八个端口都将被使用。

Base, Medium and Full Configurations的位分布

不同配置的位分布,Bit Assignments for Base Configuration

看完相关介绍,接下来就是该考虑如何用FPGA实现了,我自己实现的是在Base模式下的14bit数据接收,像素时钟为20Mhz(这个需要示波器测量,不同的摄像头它的时钟不一定一样):

1.首先将像素时钟通过锁相环倍频率成140Mhz;

2.将20Mhz时钟和140Mhz时钟送入SelectIO IP核,将数据串转并;

3.从IP核出来的28bit数据中获取相应的数据信号、FVAL帧同步信号、LVAL行同步信号。

用到了pg070-selectio-wiz当然得列出它的官方文档链接了:

https://www.xilinx.com/support/documentation/ip_documentation/selectio_wiz/v5_1/pg070-selectio-wiz.pdf

http://www.dzsc.com/xinghao/DS90CR285.html(DS90CR285/DS90CR286)

上面链接中有一个比较重要的时序:

根据这个这个时序可以知道28bit数据的组合情况,见下表

再结合位分布的表就可以准确的提取出来相关数据了

FVAL = DATA[6];

LVAL = DATA[10];

DVAL=DATA[2];

DATA_BUF = {…};这个可以根据表格自己去组了

声明:所有文章属于个人在工作中所记下和搜集的笔记,不得转载