https://mp.weixin.qq.com/s/t93z1cIuQIxDLUhsn4eCKg

于芯片而言,功耗不仅仅是耗能问题,它会严重影响可靠性、性能及成本。而对于手持设备,功耗更是必需要严肃对待的一项性能指标,待机时间与其直接相关。所以功耗在芯片诞生过程中从算法架构到设计实现到封装测试从始至终都是被热切关怀着。老生常谈:芯片80%的功耗都取决于掌控『灵魂』的算法架构部分,『劳工』只有20%的空间可以发挥。

题外话:最多只有10%的硅农是可以掌握『灵魂』的,剩下那90%就是劳工,他们夜以继日乐此不疲地搬着砖,中间几乎没有通道,一切都取决于最初的决定。那10%都是高山仰止的,驴无法企及,所以只能浅显的论述一下劳工能做的事儿。

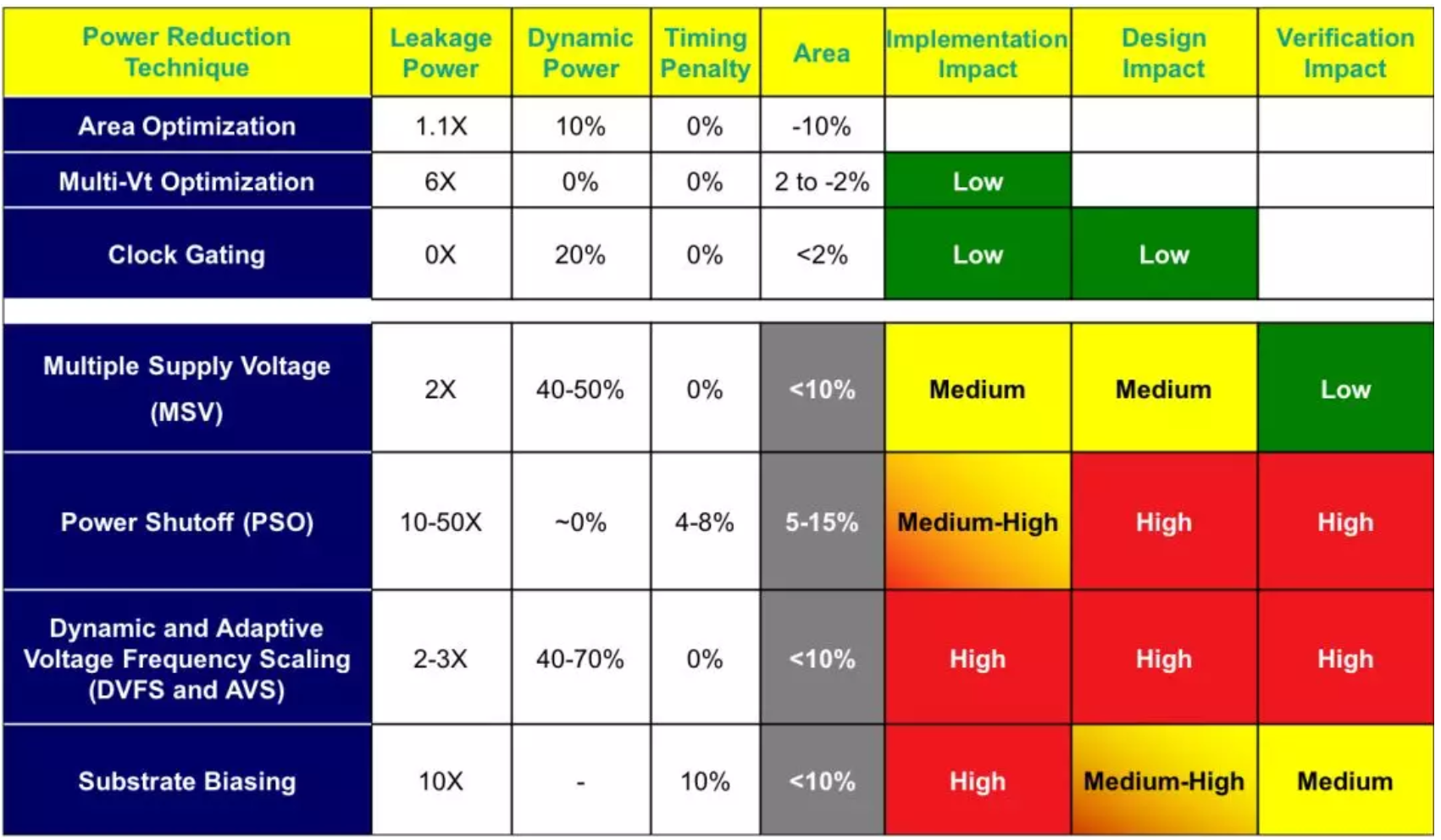

劳工们虽然触碰不到灵魂,但却不乏探索精神,他们在20%的空间内竭尽所能发挥聪明才智,探寻出了一套优化功耗的方法。下表列出了目前主流的优化功耗的方法及对设计、实现、验证各个环节的影响。论及动态功耗的优化,还是需要从动态功耗的组成及对应的计算公式入手,当工作电压和频率一定时,那优化动态功耗首要的目标就是尽量去减少toggle rate,此外对于internal power 还需要尽量减小输入pin 的transition 跟输出的load,对于负载功耗当然是尽量减小负载电容。基于此大致有如下几种优化动态功耗的方式:

-

clock gating: 到目前为止依旧是最行之有效的办法。

-

multi bit merge:需要库的支持。

-

activity driven power optimize:需要读入activty 文件

-

多电压域(MSV):需要power intent 支持。

-

动态电压频率调整(DVFS):需要power intent 支持。