版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

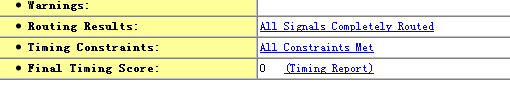

原先的时序报告:

根据时序报告中的路径提示,在ILA的某个路径上建立时间过长,而程序中并未例化ila的核,只是使用了chipscrop.。所以猜测是chipscrop部分的路径时序不收敛。

于是去除了名为AD9739_dds的chipscrop,发现时序就满足了。

证明时序是chipscrop中插入的ILA造成的时序问题。

那么重新加入chipsrop,查看设置,发现他的采样时钟时AD_CLK_out,这个时钟是未经过IDEALY的。而所采集数据所用的fifo时钟是经过IDEALY的,这样,采集时钟就造成了时序的不匹配(主要是存在时间延迟)。于是时序不满足。

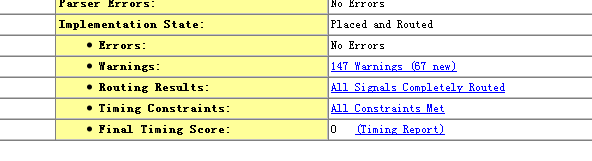

把这个时钟修改成经过IDEALY后的时钟查看时序报告。满足时序报告。

同理,不改动chipsrop的采样时钟,AD_CLK_out这个信号不经过ideay直接作为fifo的采样时钟一样可以满足时序。

PS:关于时序分析的资料,个人觉得小梅哥的文档很好。资料已经上传至本人CSDN的资源界面。