Cortex - M3处理器

总线

Cortex - M3处理器基于哈佛结构体系,拥有独立的地址总线和数据总线,分别称为I-Code总线和D-Code总线。存储范围位0x00000000~0x1FFFFFFF。

Cortex - M3处理器有一条额外的系统总线用于存取位于0x20000000~0xDFFFFFFF和

0xE0100000~0xFFFFFFFF地址范围的Cortex-M3系统控制区。

Cortex - M3处理器的片上调试系统使用一条私有设备总线来连接

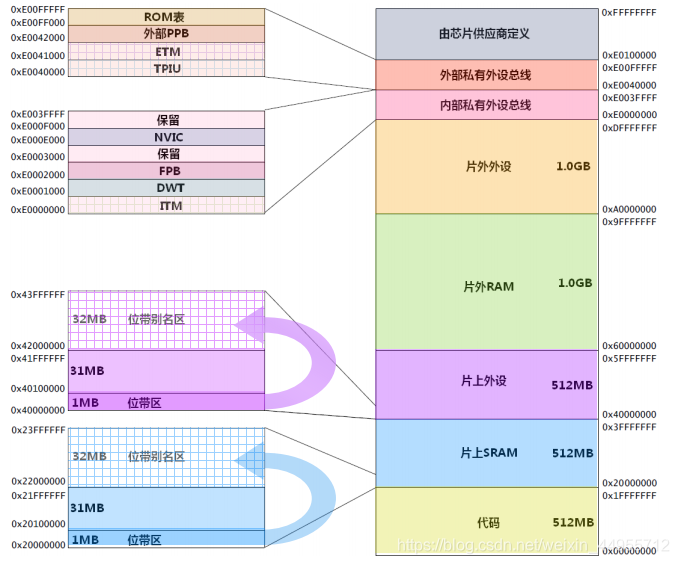

储存映射

Cortex - M3处理器拥有多重内部总线,但是存储区是一个线性4GB地址空间。

最开始1GB为Code(代码)区和SRAM(静态内存)区

Code区使用经过针对性优化的I-Code总线连接。SRAM区使用D-Code总线连接

接下来的0.5GB储存空间是片上外设区

微控制器的用户设备的基地址都落在这个区域。片上外设区和SRAM区的起始1MB区域可以使用位带技术实现位寻址。因此STM32所有的存储区都可以用于“字”或“位”位最小单位实现数据操作。

随后的2GB地址空间是拓展外部SRAM和外部设备

最后的0.5GB是Cortex - M3处理器内部设备区

位带的概念

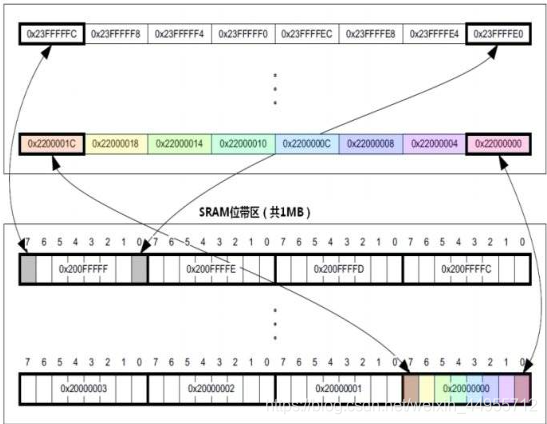

在 Cortex-M3支持的位带中,有两个区中实现了位带。

其中一个是 SRAM 区的最低 1MB 范围, 0x20000000 ‐ 0x200FFFFF(SRAM 区中的最低 1MB);

第二个则是片内外设区的最低 1MB范围, 0x40000000 ‐ 0x400FFFFF(片上外设区中的最1MB)。 这两个区中的地址除了可以像普通的 RAM 一样使用外,它们还都有自己的“位带别名区”,位带别名区把每个比特膨胀成一个 32 位的字。当你通过位带别名区访问这些字时,就可以达到访问原始比特的目的。

Cortex-M3 使用如下术语来表示位带存储的相关地址

* 位带区: 支持位带操作的地址区

* 位带别名: 对别名地址的访问最终作用到位带区的访问上(注意:这中间有一个地址映射过程)

对于SRAM中的某个比特,该比特在位带别名区的地址:

AliasAddr = 0x22000000 + ((A‐0x20000000)*8+n)*4 = 0x22000000 + (A‐0x20000000)32 + n4

对于片上外设位带区的某个比特,该比特在位带别名区的地址:

AliasAddr = 0x42000000 + ((A‐0x40000000)*8+n)*4 = 0x42000000 + (A‐0x40000000)32 + n4

系统节拍定时器

SysTick通过锁相环PLL0来提高频率提供CPU。

由于芯片总是从内部的RC振荡器开始工作,因此主振荡器只会应软件的请求而启动。

实现方法是设定SCS寄存器中的OSCEN位使能。

主振荡器提供一个状态标志SCS寄存器的OSCSTAT位,这样软件就可以确定何时主振荡器在运行稳定。

此时,软件可以控制切换到主振荡器,使其作为时钟源。

在启动以前,必须通过SCS的OSCRANGE位,选择一个频率范围。

在确定了主振荡器之后,需要进行锁相环的配置。