代码工程的GITHUB连接:点进进入GITHUB仓库

https://github.com/sj15712795029/stm32f1_marvell88w8801_marvell8801_wifi

Marvell自己实现驱动系列文章分为几篇介绍:

SDIO wifi Marvell8801/Marvell88w8801 介绍(一) ---- 芯片介绍

SDIO wifi Marvell8801/Marvell88w8801 介绍(二) ---- SDIO协议介绍

SDIO wifi Marvell8801/Marvell88w8801 介绍(三) ---- 寄存器介绍

SDIO wifi Marvell8801/Marvell88w8801 介绍(四) ---- 命令/事件/数据格式

SDIO wifi Marvell8801/Marvell88w8801 介绍(五) ---- TLV

SDIO wifi Marvell8801/Marvell88w8801 介绍(六) ---- 实现初始化功能

SDIO wifi Marvell8801/Marvell88w8801 介绍(七) ---- 实现搜索功能

SDIO wifi Marvell8801/Marvell88w8801 介绍(八) ---- 实现STA功能

SDIO wifi Marvell8801/Marvell88w8801 介绍(九) ---- 实现AP功能

SDIO wifi Marvell8801/Marvell88w8801 介绍(十) ---- 移植TCP/IP协议栈LWIP

SDIO wifi Marvell8801/Marvell88w8801 介绍(十一) ---- 自己编写LWIP没有的DHCP server

SDIO wifi Marvell8801/Marvell88w8801 介绍(十二) ---- MQTT介绍

SDIO wifi Marvell8801/Marvell88w8801 介绍(十三) ---- 百度云操作说明

SDIO wifi Marvell8801/Marvell88w8801 介绍(十四) ---- 上位机STA操作/代码

SDIO wifi Marvell8801/Marvell88w8801 介绍(十五) ---- 上位机AP操作/代码

SDIO wifi Marvell8801/Marvell88w8801 介绍(十六) ---- 上位机UDP操作/代码

SDIO wifi Marvell8801/Marvell88w8801 介绍(十七) ---- 上位机TCP操作/代码

SDIO wifi Marvell8801/Marvell88w8801 介绍(十八) ---- 上位机PING操作/代码

SDIO wifi Marvell8801/Marvell88w8801 介绍(十九) ---- 上位机云服务器(百度云)操作/代码

每篇更新打开专栏可以看到:打开Marvell8801/Marvell8801 专栏

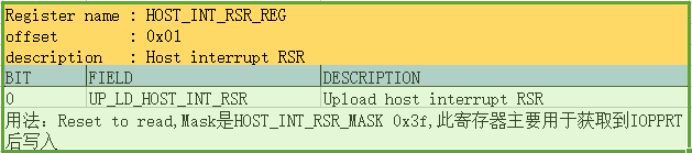

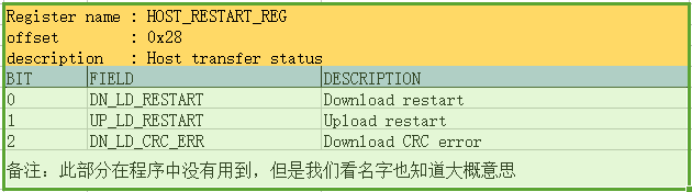

因为目前市面上找不到Marvell8801寄存器的定义,所以我根据代码自己整理了一份,供大家参考使用:

SDIO的FUNC0寄存器我们已经在SDIO协议中介绍了,Wi-Fi card的FUNC1就是vendor定的,而且即使一家vendor根据每个Wi-Fi型号的不同每个register address功能也不同,所以我们最好能拿到register手册,很遗憾,我也没有,但是不要灰心,我们可以通过另外一个途径获取到,驱动中有一个文件叫做:mlan_sdio.h,这个对我们来说就是活生生的register的手册,以下是我通过这个文件整理的,下面我们进行一个个介绍

以上寄存器也仅仅作为查阅使用,至于有不懂的,后续驱动介绍的时候会让你重新印象深刻

对应的驱动寄存器代码如下:

/* Host Control Registers */

/** Host Control Registers : Host to Card Event */

#define HOST_TO_CARD_EVENT_REG 0x00

/** Host Control Registers : Host terminates Command 53 */

#define HOST_TERM_CMD53 (0x1U << 2)

/** Host Control Registers : Host without Command 53 finish host */

#define HOST_WO_CMD53_FINISH_HOST (0x1U << 2)

/** Host Control Registers : Host power up */

#define HOST_POWER_UP (0x1U << 1)

/** Host Control Registers : Host power down */

#define HOST_POWER_DOWN (0x1U << 0)

/** Host Control Registers : Host interrupt RSR */

#define HOST_INT_RSR_REG 0x01

/** Host Control Registers : Upload host interrupt RSR */

#define UP_LD_HOST_INT_RSR (0x1U)

#define HOST_INT_RSR_MASK 0x3F

/** Host Control Registers : Host interrupt mask */

#define HOST_INT_MASK_REG 0x02

/** Host Control Registers : Upload host interrupt mask */

#define UP_LD_HOST_INT_MASK (0x1U)

/** Host Control Registers : Download host interrupt mask */

#define DN_LD_HOST_INT_MASK (0x2U)

/** Enable Host interrupt mask */

#define HIM_ENABLE (UP_LD_HOST_INT_MASK | DN_LD_HOST_INT_MASK)

/** Disable Host interrupt mask */

#define HIM_DISABLE 0xff

/** Host Control Registers : Host interrupt status */

#define HOST_INT_STATUS_REG 0x03

/** Host Control Registers : Upload host interrupt status */

#define UP_LD_HOST_INT_STATUS (0x1U)

/** Host Control Registers : Download host interrupt status */

#define DN_LD_HOST_INT_STATUS (0x2U)

/** Host Control Registers : Download and Upload host interrupt status */

#define INT_STATUS_ALL (UP_LD_HOST_INT_STATUS | DN_LD_HOST_INT_STATUS)

/** Port for registers */

#define REG_PORT 0

/** LSB of read bitmap */

#define RD_BITMAP_L 0x04

/** MSB of read bitmap */

#define RD_BITMAP_U 0x05

/** LSB of write bitmap */

#define WR_BITMAP_L 0x06

/** MSB of write bitmap */

#define WR_BITMAP_U 0x07

/** LSB of read length for port 0 */

#define RD_LEN_P0_L 0x08

/** MSB of read length for port 0 */

#define RD_LEN_P0_U 0x09

/** Ctrl port */

#define CTRL_PORT 0

/** Ctrl port mask */

#define CTRL_PORT_MASK 0x0001

/** Data port mask */

#define DATA_PORT_MASK 0xfffe

#define MAX_PORT 16

/** Misc. Config Register : Auto Re-enable interrupts */

#define AUTO_RE_ENABLE_INT MBIT(4)

/** Host Control Registers : Host transfer status */

#define HOST_RESTART_REG 0x28

/** Host Control Registers : Download CRC error */

#define DN_LD_CRC_ERR (0x1U << 2)

/** Host Control Registers : Upload restart */

#define UP_LD_RESTART (0x1U << 1)

/** Host Control Registers : Download restart */

#define DN_LD_RESTART (0x1U << 0)

/* Card Control Registers */

/** Card Control Registers : Card to host event */

#define CARD_TO_HOST_EVENT_REG 0x30

/** Card Control Registers : Card I/O ready */

#define CARD_IO_READY (0x1U << 3)

/** Card Control Registers : CIS card ready */

#define CIS_CARD_RDY (0x1U << 2)

/** Card Control Registers : Upload card ready */

#define UP_LD_CARD_RDY (0x1U << 1)

/** Card Control Registers : Download card ready */

#define DN_LD_CARD_RDY (0x1U << 0)

/** Card Control Registers : Host interrupt mask register */

#define HOST_INTERRUPT_MASK_REG 0x34

/** Card Control Registers : Host power interrupt mask */

#define HOST_POWER_INT_MASK (0x1U << 3)

/** Card Control Registers : Abort card interrupt mask */

#define ABORT_CARD_INT_MASK (0x1U << 2)

/** Card Control Registers : Upload card interrupt mask */

#define UP_LD_CARD_INT_MASK (0x1U << 1)

/** Card Control Registers : Download card interrupt mask */

#define DN_LD_CARD_INT_MASK (0x1U << 0)

/** Card Control Registers : Card interrupt status register */

#define CARD_INTERRUPT_STATUS_REG 0x38

/** Card Control Registers : Power up interrupt */

#define POWER_UP_INT (0x1U << 4)

/** Card Control Registers : Power down interrupt */

#define POWER_DOWN_INT (0x1U << 3)

/** Card Control Registers : Card interrupt RSR register */

#define CARD_INTERRUPT_RSR_REG 0x3c

/** Card Control Registers : Power up RSR */

#define POWER_UP_RSR (0x1U << 4)

/** Card Control Registers : Power down RSR */

#define POWER_DOWN_RSR (0x1U << 3)

/** Card Control Registers : SQ Read base address 0 register */

#define READ_BASE_0_REG 0x40

/** Card Control Registers : SQ Read base address 1 register */

#define READ_BASE_1_REG 0x41

/** Card Control Registers : Card revision register */

#define CARD_REVISION_REG 0x5c

/** Firmware status 0 register (SCRATCH0_0) */

#define CARD_FW_STATUS0_REG 0x60

/** Firmware status 1 register (SCRATCH0_1) */

#define CARD_FW_STATUS1_REG 0x61

/** Firmware ready */

#define FIRMWARE_READY 0xfedc

/** Rx length register (SCRATCH0_2) */

#define CARD_RX_LEN_REG 0x62

/** Rx unit register (SCRATCH0_3) */

#define CARD_RX_UNIT_REG 0x63

/** Card Control Registers : Card OCR 0 register */

#define CARD_OCR_0_REG 0x68

/** Card Control Registers : Card OCR 1 register */

#define CARD_OCR_1_REG 0x69

/** Card Control Registers : Card OCR 3 register */

#define CARD_OCR_3_REG 0x6A

/** Card Control Registers : Card config register */

#define CARD_CONFIG_REG 0x6B

/** Card Control Registers : Miscellaneous Configuration Register */

#define CARD_MISC_CFG_REG 0x6C

/** Card Control Registers : Debug 0 register */

#define DEBUG_0_REG 0x70

/** Card Control Registers : SD test BUS 0 */

#define SD_TESTBUS0 (0x1U)

/** Card Control Registers : Debug 1 register */

#define DEBUG_1_REG 0x71

/** Card Control Registers : SD test BUS 1 */

#define SD_TESTBUS1 (0x1U)

/** Card Control Registers : Debug 2 register */

#define DEBUG_2_REG 0x72

/** Card Control Registers : SD test BUS 2 */

#define SD_TESTBUS2 (0x1U)

/** Card Control Registers : Debug 3 register */

#define DEBUG_3_REG 0x73

/** Card Control Registers : SD test BUS 3 */

#define SD_TESTBUS3 (0x1U)

/** Host Control Registers : I/O port 0 */

#define IO_PORT_0_REG 0x78

/** Host Control Registers : I/O port 1 */

#define IO_PORT_1_REG 0x79

/** Host Control Registers : I/O port 2 */

#define IO_PORT_2_REG 0x7A