基于FPGA的数字钟——(三)数码管显示模块

硬件原理

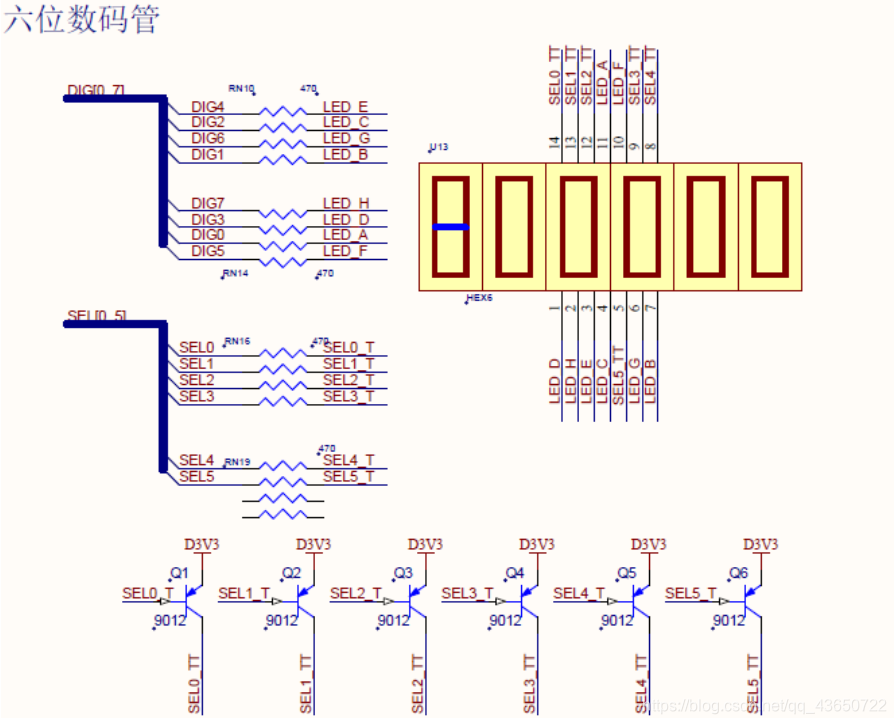

本设计中使用 6 个共阳数码管,可以显示 6 个数字(包含小数点) 。电路用 PNP管来反向驱动并且控制列扫描信号来选择哪个数码管。而且所有的 6 个数码管的“段选信号”(LEDA … LEDH)都共用驱动引脚(LED_A~LEDH)。数码管的所有驱动信号都是“低电平有效”。具体的原理图设计如下图所示:

数码管扫描原理

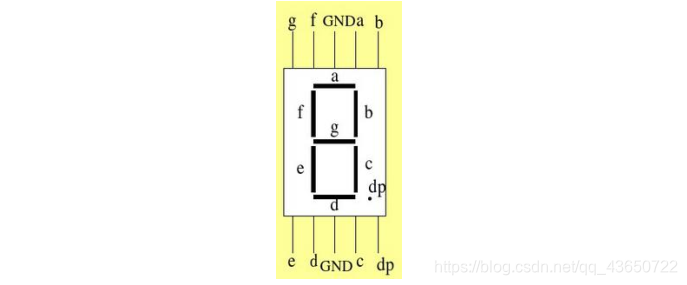

单个数码管可以采用静态显示方式,如图所示,数码管被分成 a、 b、 c、 d、e、 f、 g 和小数点,每段可以单独控制亮灭,通过点亮不同的段显示不同的数字和字符。

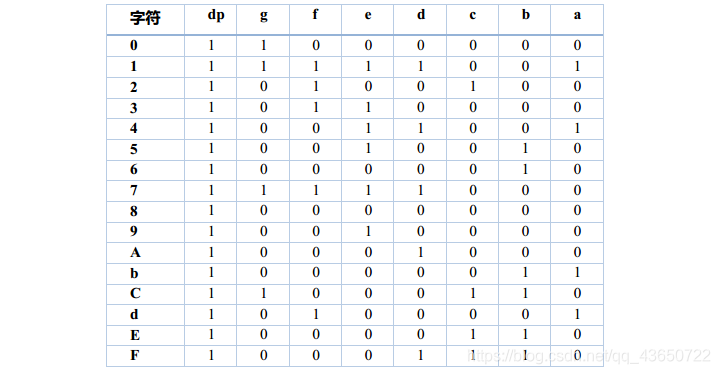

其编码表如下

驱动原理

依照一定的频率位选各数码管,利用人的视觉暂留来达到视觉上的连续感。

Verilog代码

//////////////////////////////////////////////////////////////////////////////////

// Company: NanJing University of Information Science & Technology

// Engineer: Yang Cheng Yu

//

// Create Date: 2019/12/29 15:55:40

// Design Name: seg_decoder

// Module Name: seg_decoder

// Project Name: Clock

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module seg_decoder

(

input clk,

input rst,

input[3:0] bin_data, // bin data input,0-f

output reg[6:0] seg_data // seven segments LED output

);

always@(posedge clk or negedge rst)

begin

if(!rst)

seg_data <= 7'b111_1111;

else

case(bin_data)

4'd0:seg_data <= 7'b100_0000;

4'd1:seg_data <= 7'b111_1001;

4'd2:seg_data <= 7'b010_0100;

4'd3:seg_data <= 7'b011_0000;

4'd4:seg_data <= 7'b001_1001;

4'd5:seg_data <= 7'b001_0010;

4'd6:seg_data <= 7'b000_0010;

4'd7:seg_data <= 7'b111_1000;

4'd8:seg_data <= 7'b000_0000;

4'd9:seg_data <= 7'b001_0000;

4'ha:seg_data <= 7'b000_1000;

4'hb:seg_data <= 7'b000_0011;

4'hc:seg_data <= 7'b100_0110;

4'hd:seg_data <= 7'b010_0001;

4'he:seg_data <= 7'b000_0110;

4'hf:seg_data <= 7'b000_1110;

default:seg_data <= 7'b111_1111;

endcase

end

endmodule

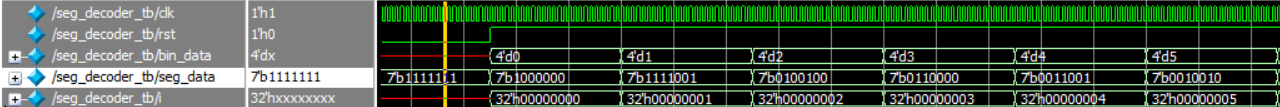

仿真波形(部分)