quartus的创建并与开发版连接

quartus的创建

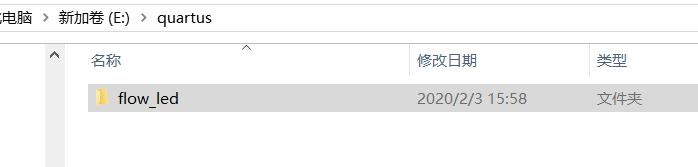

首先新建一个文件夹

在改文件夹下新建四个文件夹

然后双击quartus打开软件

点击 File --> New Project Wizard

点击 Next,将工程放在刚才创建的文件夹内,如下图所示,工程名字命名为flow_led(第二行位工程名)

继续点击 Next

因为是新建工程,所以直接点击next

这一步,选择板子对应的型号

这是我板子的型号,点击Next

接着点击 Next

点击Finish

在点击 File -->New

在点击 File -->New

选中 Verilog HDL File

在这里面粘贴流水灯代码

module flow_led(

input sys_clk , //系统时钟

input sys_rst_n, //系统复位,低电平有效

output reg [3:0] led //4个LED灯

);

//reg define

reg [23:0] counter;

//*****************************************************

//** main code

//*****************************************************

//计数器对系统时钟计数,计时0.2秒

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

counter <= 24’d0;

else if (counter < 24’d1000_0000)

counter <= counter + 1’b1;

else

counter <= 24’d0;

end

//通过移位寄存器控制IO口的高低电平,从而改变LED的显示状态

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

led <= 4’b0001;

else if(counter == 24’d1000_0000)

led[3:0] <= {led[2:0],led[3]};

else

led <= led;

end

endmodule

ctrl + s保存,或点击左上角的保存图标

将文件保存在刚开始创建的rtl文件夹下

点击上图红色圈内的图标

点击上图红色圈内的图标

接下来,进行文本编辑器设置设置Tools–>options,点击Text Editor

更改效果如下

改变双引脚功能

双击上图芯片型号

选择 Device and Options,然后选择下图点击的双用途引脚

将nCEO 改为普通引脚

接下来分配引脚,与开发版IO分配进引脚对应,选择 Assignments–>Pin Planner

开发版的功能引脚类似如下图所示

直接输入字母和数字按回车,例如输入 M11 后按回车

点击关闭。

在par文件夹下会生成.qsf管脚信息文件,如下图

打开该文件,为下图所示

以后如果要更改管脚,可以直接在该文件下更改。

编译整个工程

在下图右边查看整个编译进度

将板子和电脑连接,连接电源线,打开电源,将程序下载到板子上,选择 Tools --> Programmer,或直接点击图标

得到下图

如果想让开发版一直保存程序,需要以下操作,选择file -->Convert Programming File

点击左下角 Flash Loader 再点击对应右边的 Add Device,根据板子型号选择

再选择 SOF Data ,然后点击 Add File,选择.sof文件

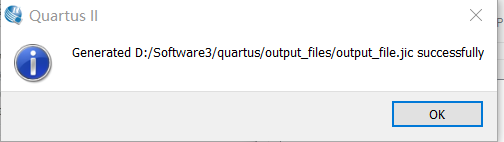

配置好之后,点击Generate

点 OK

点击close退出此界面

重新打开下图界面

删除原来的sof文件

然后 点击 Add File

选择新生成的jic文件

选中Program/Configure 然后点击 Start