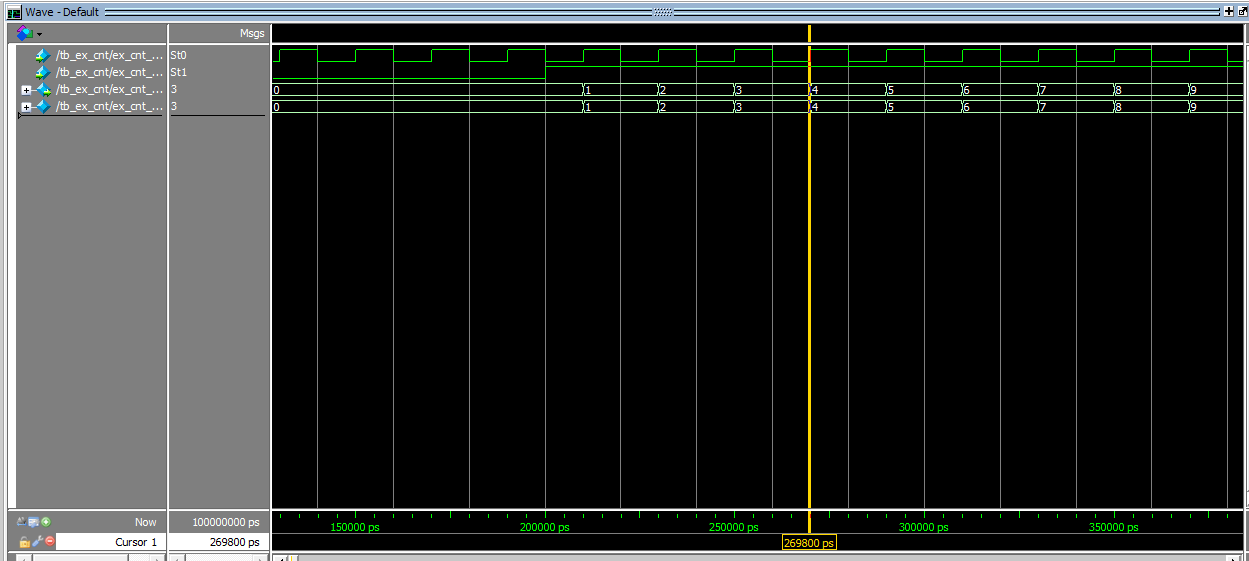

//仿真激励 testbench `timescale 1ns/100ps //#10.11 --->延时10.10ns 预编译声明延时单位 单位时标 module tb_ex_cnt;//声明不需要端口列表 reg tb_sclk, tb_rst_n;//激励信号的声明 wire [9:0] tb_cnt;//原始模块输出信号连接线的声明 initial //一次上电只被执行一次 begin //initial 快内只能对寄存器变量赋值 tb_sclk <= 0; tb_rst_n <= 0; #200.1 tb_rst_n <= 1; end always #10 tb_sclk <= ~tb_sclk;//循环震荡周期为20ns //例化的方法 //原始模块名字 例化的名字(可以自定义) ex_cnt ex_cnt_inst( .sclk (tb_sclk),//模拟晶振产生时钟震荡 .rst_n (tb_rst_n),//模拟外部复位电平 .cnt (tb_cnt) //例化模块的时候如果原始模块是输出信号,那么括号内必须是wire变量 ); endmodule

----------------来源ModelSim 仿真