作者:AirCity 2020.2.4

[email protected] 本文所有权归作者Aircity所有

1 Memory Map

MPC8270内部memory space=256KB,有32bit地址线,可以映射4G空间。

这256KB包括了8270的所有寄存器,它在4G空间中的位置,由IMMR决定。过程如下:

CPU复位后,根据Hardware Configuration Word寄存器中ISB[13:15]的值,职位IMMR中ISB[0:13]的值,辞职纪委MPC8270内部memory space的默认初始地址。软件根据此默认地址,改写ISB值,之后internal memory space被重新映射,IMMR也就有了新的地址。

2 保护机制

- 校验,包括奇偶校验,mask number等。奇校验是加1位,使所有bit中1的个数为奇数。偶校验是加1位,使所有bit中1的个数为偶数。MPC8270的address和data线都有奇偶校验,并且data bus校验有普通,read-modify-write,ECC correction三种校验模式。

- 60X Bus Monitor:当一个Transaction开始(TSn),Bus monitor开始计数,一直等到a data beat is acknowledge(TAn),然后开始下一个计数。当对于address only transaction,Bus Monitor 开始计数直到收到AACKn信号,之后开始下一次计数。如超时,将会使能TEAn信号。如果地址Bus Monitor 使能AACKn,a core machine check or reset interrupt会被产生(计数超时值在SYPCR[BMT]中)

- Local Bus Monitor与60x Bus Monitor类似。

完善的保护机制使PowerPC常被用于航空航天领域。

2.1 ECC

Error Checking and Correction,即错误检查和纠正。它能发现2bit错误或纠正1bit错误。算法比较复杂。记住以下规律即可:

8bit数据位需要额外的5bit来进行ECC,每增加1倍数据位,ECC就要增加1bit,例如32bit数据位需要额外的7bit来进行ECC,64bit数据位需要额外的8bit来进行ECC。PowerPC的数据线是72根,其中8根是用来做ECC校验的。

3 某量产项目的memory map

0xFE00 0000 存放bootstrape

0xFE20 0000 存放default configuration table

0x0100 0000 存放operation configuration table

0x02000000 存放operation software

MPC8270启动后,根据Hardware Configuration Word 的BMS位配置BR0[BA]:

BMS=0,BR0[BA]=0xFE00 0000~0xFFFF FFFF;

BMS=1,BR0[BA]=0x0000 0000~0x01FF FFFF;

4 上电顺序

Core电压:VDD=1.5V

PLL等电路电压:VCCYSN=1.5V

IO电压:VDDH=3.3V

VIN=0~3.6V

复位时要求:

(a) VDD&VCCSYN大于VDDH 0.4V不超过100ms

(b) VDDH大于VDD&VCCSYN 3.3V不能超过100ms

也就是说VDD,VCCSYN和VDDH要几乎同时上电。前后不能差100ms

正常工作时:

(a) VDD@VCCSYN不能超过VDDH 0.4V

(b) VDDH不能超过VDD&VCCSYN 2.5V

© VINH任何时候都不能大于VDDH 2.5V

推荐的上电顺序:

VDD&VCCSYN(0~100ms以内)VDDHVIN,这要求MPC8270在完成上电以前,其他芯片不能有输出电压给它。

5 上电复位载入配置字(HRCW)的流程

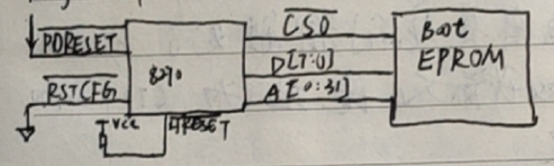

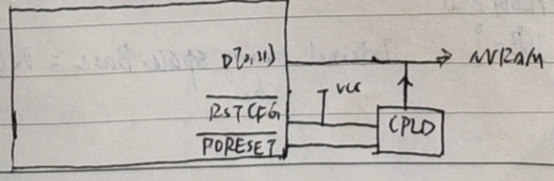

① 使能PORESETn(>16 clockin)

② PORESETn上升沿采样RSTCFGn,若为低,则8270位master,若为高则为slave

③ 若为master,则读取Boot ROM中的数据,先读32bit配置master,再读32bit配置第一个slave,一直配置完8个为止。若为slave,则等待一个RST_CFGn的低脉冲,在地脉冲期间,读D[0:31]上的电平,作为配置字。

④ 根据配置字启动。

注意:HRESETn也能重新载入32bit HRCW(硬件配置字),但不能改变clock mode(modck_H[0:3]+modck_L[])

举例:

- 单8270,Master,8270仍然以为有7个slave,一直配置完8个slave为止

- 多个8270,Master

- 单个8270 Slave

6 载入HRCW后,载入程序的过程

PORESETn,HRESETn,SRESETn都能使8270重新载入EPROM启动,原因是他们都触发了System Reset。System Reset后,CPU的入口地址是CIP+00100,CIP由HRCW决定。

对HRCW的解释如下

| bit | 内容 | 解释 |

| 0 | EARB=0 | 内部仲裁,60x bus的控制权由内部决定。当使用L2 Cache或多个8270时,他们的60x线在一起,需要争夺bus master仲裁者来接受BRn信号,给出BGn信号使其成为Master |

| 1 | EXMC=0 | 内部memory controller |

| 2 | CDIS=0 | core is active |

| 3 | EBM=0 | sigle MPC8270 bus mode |

| 4-5 | BPS=01 | 8bit size for boot |

| 6 | CIP=0 | Exception Vectored to 0xFFFn_nnnn |

| 7 | ISPS=0 | 作为slave时,外部访问Internal space的port size |

| 8-9 | L2CPC=00 | L2 Cache PIN config |

| 10-11 | DPPC=00 | data parity pins configuration |

| 12 | PLLBP=0 | |

| 13-15 | ISB=010 | Internal Memory Space Base=0x0F00_0000 |

| 16 | BMS=0 | Boot Memory Space = 0xFE00_0000~0xFFFF_FFFF |

| 17 | BBD=0 | Bus busy disable PIN definition |

| 18-19 | MMR =00 | No Masking on bus request line |

| 20-21 | LBPC=01 | Local bus pins function as PCI bus |

| 22-23 | APPC=10 | Address parity pins definition |

| 24-25 | CS10PC=00 | |

| 26 | ALD_EN=0 | CP auto load is disable |

| 27 | 0 | |

| 28-31 | MODCK_H=1000 |