Table of Contents

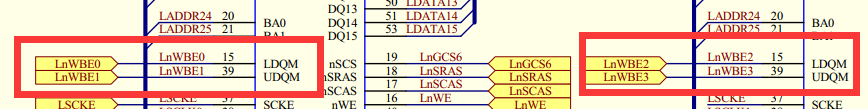

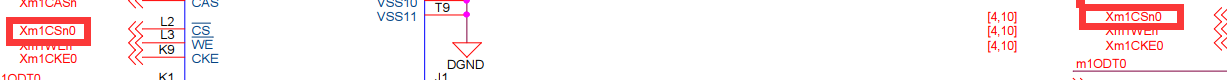

1.3.1、jz2440级联接法(高16bit 低16bit)方式

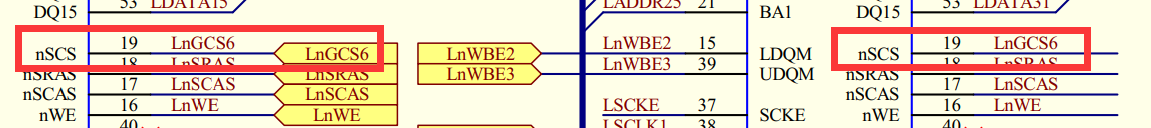

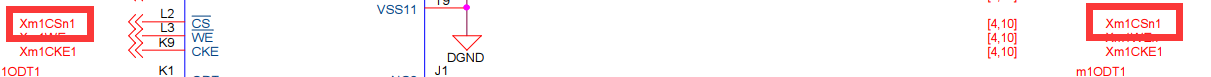

1.3.2、tiny4412级联接法(0~7 16~23 / 8~15 24~31bit )错开方式

一、原理图解析

1.1、jz2440

1.1.1、jz2440引脚说明

1.1.2、地址(ADDR)引脚说明

13根地址线(行列地址共用线)(因为内存控制器寻址方式是先发出行地址,再发出列地址)

(查数据手册行地址数为13,列地址数为9)

1.1.3、Bank引脚说明

DRAM内部由多个bank组成,目的是一块一块动态循环刷新,而不需要一下刷新整块内存,因此可以降低功耗

内存控制器在寻址之前必须先通过bank线发出信号,选择内存条里面的哪个bank

jz2440有2根bank线,因此bank块数=2^2=4块

1.1.4、DQM引脚说明

DQM就是掩码控制位,在sdram中每个DQM控制8bit Data。在读操作的时候没什么大的影响,比如读32位的sdram module,但只要其中低8bit的数据,没有关系,只要读出32bit数据,再在软件里将高24位bit和0“与”就可以了,有没有DQM关系不大。但在执行写操作时。如果没有DQM就麻烦了,可能在软件上是写一个8bit数据,但实际上32根数据线是物理上连接到SDRAM的,只要WR信号一出现,这32位就会写sdram中去,高24bit数据就会被覆盖。通过使用DQM就可以将其对应的8bit屏蔽,不会因为写操作而覆盖数据了。

1.1.5、片选(CS)说明(决定寻址起始地址)

内存控制器可以控制多块存储芯片,具体选择哪块要根据片选信号决定

jz2440选择的是LnGCS6

起始地址:0x30000000

1.1.2、jz2440内存大小计算方法

一片内存的大小size(字节) = 2^(13Row+9Column)*4(bank)*(16bit/2)=32MB

1.2、tiny4412

tiny4412上面接有4片内存颗粒,每2片16位组成一块32位逻辑上的一片内存条,

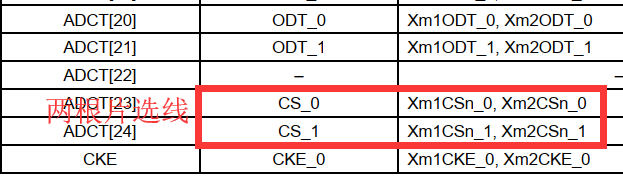

4片内存颗粒组成2块内存条,正好接2根片选线(CS0 CS1)

1.2.1、tiny4412引脚说明

1.2.2、DQS引脚说明

DQS信号主要用来在一个时钟周期内准确区别每个传输周期,并便于接收方准确接受数据,它是双向的,在数据写入内存时,DQS信号由内存控制器发出,在读出数据时,DQS信号由DDR芯片内部发出通知控制器接受数据,说白了它就是数据同步信号

1.2.3、片选(CS)说明(决定寻址起始地址)

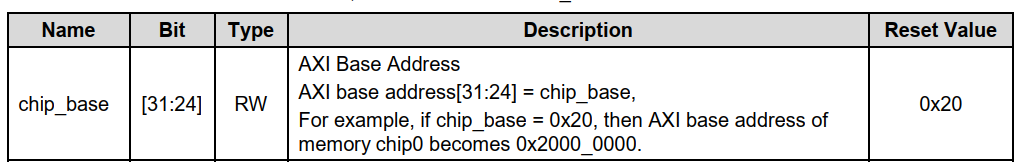

起始地址:0x40000000 (有别于jz2440,这个需要通过寄存器MEMCONFIG0/1配置)

起始地址:0x60000000 第一块起始地址0x40000000+0x20000000(512MB第一块大小)=0x60000000

1.3、内存颗粒级联说明

一般内存颗粒以16位的居多,一般是级联成一块32位的内存条

32位=4字节 4个字节怎么分配?

可以分配高16位给第一片,低16位给第二片,也可以错开分配,数据引脚的连线必须和DQM DQS同步

1.3.1、jz2440级联接法(高16bit 低16bit)方式

1.3.2、tiny4412级联接法(0~7 16~23 / 8~15 24~31bit )错开方式

二、读写控制原理

2.1、内存控制器怎么寻址 ?

- 问题1:怎样访问里面的某个格子呢?

1. 首先发出一个片选信号,选中整个芯片;

2. 发出Bank地址,选择是哪一个Bank(块,即表格);

3. 发出行地址;

4. 最后发出列地址,才能选中是个格子;

2.1、地址范围的确定

jz2440:

开发板中使用两片16位的SDRAM芯片并联组成32位的位宽,与CPU的32根数据线(DATA0—DATA31)相连。 BANK6的起始地址为0x30000000,所以SDRAM的访问地址为0x30000000~低0x33FFFFFF,共64MB。

tiny4412:

chip0: 0x40000000~0x5FFFFFFF chip1: 0x60000000~0x7FFFFFFF 共1GB需要通过寄存器配置

详细解析上面片选部分已经说明,不再赘述