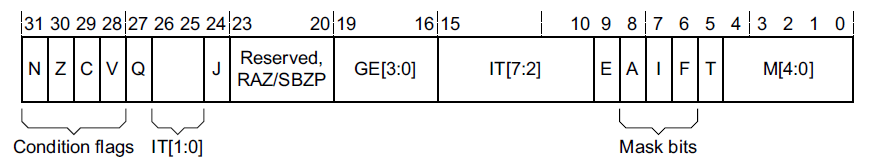

在ARMv8架构中,使用PSTATE用来描述当前处理器的状态信息。如下的图描述了PSTATE的每个字段的意义

上面是PSTATE的各个bit位的含义,我们可以将其分为三组

- 状态标志位

- N

- Z

- C

- V

- 异常状态控制位

- SS

- IL

- nRW

- EL

- SP

- 异常屏蔽位

- D

- A

- I

- F

下面来详细描述下各个字段的含义:

- 状态标志位

- N(Negative)代表的是当前指令的结果,如果是1则是负数,如果是0则是正数或者0

- Z(Zero)代表当前指令指令的结果,如果是1则是-0,否则是其他

- C(Carry Condition flag)携带环境标志,1代表携带,0代表没有

- V(Overflow Condition flag)溢出标志位,1代表溢出,0没有

- 异常屏蔽位

- D(Debug exception Mask bit)

- A(SError Interrupt mask bit)

- I(IRQ interrupt mask bit)

- F(FIQ interrupt mask bot)

- 对每个状态,1代表屏蔽,0代表没有屏蔽

访问PSTATE的各个bit位

在ARMv8-A中可以使用特殊功能的寄存器MRS对PSTATE进行读,使用MSR寄存器来对PSTATE进行写操作

ARMv8提供了一些特殊的寄存器,可以直接来操作PSTATE的各个域

比如可以直接使用NZCV来直接操作NZCV各个bit的值

通用在ARMv7中使用的是CPSR寄存器来描述处理器的状态,只不过在ARMv8-A中已经取消了CPSR寄存器

下来看下ARMv7中CPSR寄存器的格式

其中NZCV和AIF和ARMv8是保持一致的。别的位不说了,有兴趣的可以去看armv7的手册

举例说明:

比如内核中的disable_local_irq和enable_local_irq的在ARM64架构的最终实现,就是通过daifset和daifclr指令实现的

static inline void arch_local_irq_enable(void)

{

asm volatile(

"msr daifclr, #2 // arch_local_irq_enable"

:

:

: "memory");

}

static inline void arch_local_irq_disable(void)

{

asm volatile(

"msr daifset, #2 // arch_local_irq_disable"

:

:

: "memory");

}