存储器

ROM

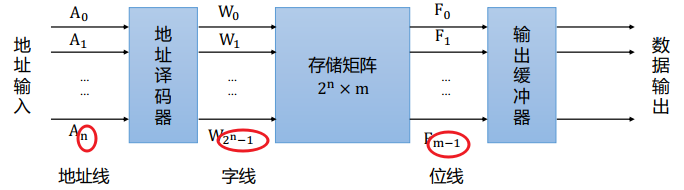

字线,存储空间里第几个字

位线 一个字几位

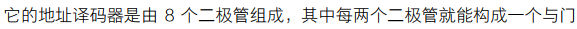

电路结构组成

地址线上两个二极管截止的通路为字选.该通路的位可以是1,否则对应的位为0

如图中W2选中时候,只有D2接了二极管,导通,D2为1,其他为接地0电势。

PROM

字线位线之间全加了二极管和可熔断熔丝,默认全部置1.

要存入0,熔断即可。

EPROM

erasable programmable read only memory

使用紫外线或者X射线,整体擦除10-20min,

EEPROM

electrically

10ms,重复擦除次数1W+,可整可零擦

RAM

sram dram

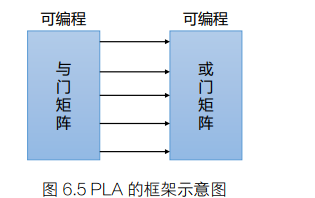

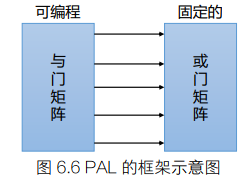

PAL PLA

改进PROM

任意一个组合逻辑都可以用“与—或”表达式来描述

GAL

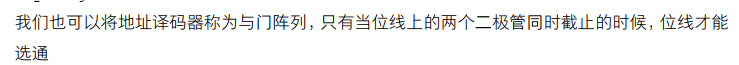

FPGA CPLD

大规模集成电路

- LAB逻辑阵列块

- 宏单元Macro cells

- 可编程连线PIA(interface array)

- IO控制块

complex programmable logic device

改进GAL

LAB由宏单元构成

包含了与门阵列和或门阵列

FPGA

FPGA 是半定制电路。

LAB单元为LE

使用lut,可编程寄存器,进位链 寄存器链

IOB 分组

布线 :连线盒CB 开关盒SB 行列连线

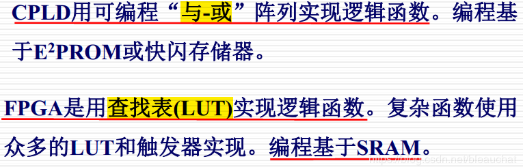

对比

1、逻辑结构不同

CPLD:类似 PAL、GAL,拥有丰富的组合逻辑电路资源。

FPGA:类似门阵列,拥有丰富的触发器、存储器资源;CPU、DSP等IP核。

2、集成度不同

CPLD:500 ~ 50000 门

3、互连结构不同

CPLD:等长度的互连线资源,其特点是延时相等。

FPGA:长度不等的多段分布式互连,其特点是布线灵活,但延时与系统布局、 布线有关。

5、粒度大小不同

FPGA为细粒度结构,CPLD为粗粒度结构。

FPGA内部有丰富连线资源,CLB分块较小,芯片的利用率较高。CPLD的宏单元的与或阵列较大,通常不能完全被应用,且宏单元之间主要通过高速数据通道连接,其容量有限,限制了器件的灵活布线,因此CPLD利用率较FPGA器件低。

6、应用范围的不同

数字逻辑系统分为两大类:

(1)控制密集型(逻辑密集型),对数据处理能力要求低,但逻辑关系复杂,输入输出较多,适合用CPLD实现。

(2)数据密集型,需要大量的数据处理能力,但逻辑相对简单,对输入要求少,适合FPGA实现。

7、配置不同

CPLD:采用EPROM,E2PROM工艺,直接写入,保密性好。

FPGA:采用SRAM工艺,故需外加ROM芯片,用于存储配置信息。其保密性较差。可实现动态重构。高端FPGA具备加密功能