一次性可编程器件(融保险丝实现)

- 一次性可编程器件(One-Time Programmable Device,简称 OTP)是一种在制造后仅能编程一次的存储设备。OTP器件在编程后数据不可更改。这些器件在很多应用场景中具有独特的优势和用途。

示例

-

MMI 16R6

-

可编程元件(显示为保险丝,下图中的波浪线)将真实输入和补码输入连接到与门。这些与门(也称为乘积项,下图中的面包片)通过“或”(下图中最右侧的圆形三角形)运算在一起,形成乘积和逻辑阵列。

类型

- PROM (Programmable Read-Only Memory)

- 熔丝型 PROM:通过熔断内部熔丝来编程。这种方法可以通过高电压来破坏选定熔丝,从而改变存储的数据。

- 反熔丝型 PROM:使用反熔丝技术,通过特定方法在特定位置创建导电路径。

特性

- 不可擦除:OTP器件一旦编程,数据即固定,无法通过任何手段擦除或重新编程。

- 高可靠性:由于数据不可更改,OTP器件在安全性和数据保持方面具有很高的可靠性,适用于需要永久保存数据的场合。

- 低成本:相比于可擦写的存储器,OTP器件在制造和材料成本上通常较低,适用于大批量生产和一次性应用。

多次擦写的可编程逻辑设备(EPROM)

示例

+----------------------------------+

| UVEPROM Chip |

| |

| +----------------------------+ |

| | Silicon Die | |

| | | |

| | +--------------------+ | |

| | | 浮栅 MOSFET | | |

| | | Transistors | | |

| | +--------------------+ | |

| | | |

| +----------------------------+ |

| |

| Transparent Quartz Window |

+----------------------------------+

原理

- 编程:

使用专用编程器将数据写入UVEPROM。在编程过程中,高电压(通常为12.5V至21V)被施加到存储单元以改变浮栅电荷状态,从而存储数据。场效应晶体管的开关状态由晶体管控制栅极上的电压控制。当电压施加到栅极时,晶体管内会形成一条传导路径,从而打开开关。在浮置栅极上存储电荷与向栅极施加电压具有相同的效果,从而允许存储数据。 - 擦除(紫外线,UV,ultraviolet):

UVEPROM芯片通常具有一个透明的石英窗,通过这个窗口,可以将芯片暴露在紫外光下。紫外光会提供足够的能量,使浮栅上的电荷逸出,从而将存储单元恢复到未编程状态(通常是逻辑高电平)。通常需要几分钟到二十分钟的紫外光照射才能完成擦除过程。

多次擦写的可编程逻辑设备(EEPROM)

示例

- electrically erasable programmable read-only memory

原理

-

编程:编程时,通过施加高电压(通常在12V左右)在控制栅和源极之间,使电子通过隧道效应被注入到浮栅上,从而改变浮栅的电荷状态,这会影响晶体管的阈值电压,从而表示存储的数据位。

-

擦除:擦除时,通过施加反向高电压,使浮栅上的电荷逸出,恢复到未编程状态。

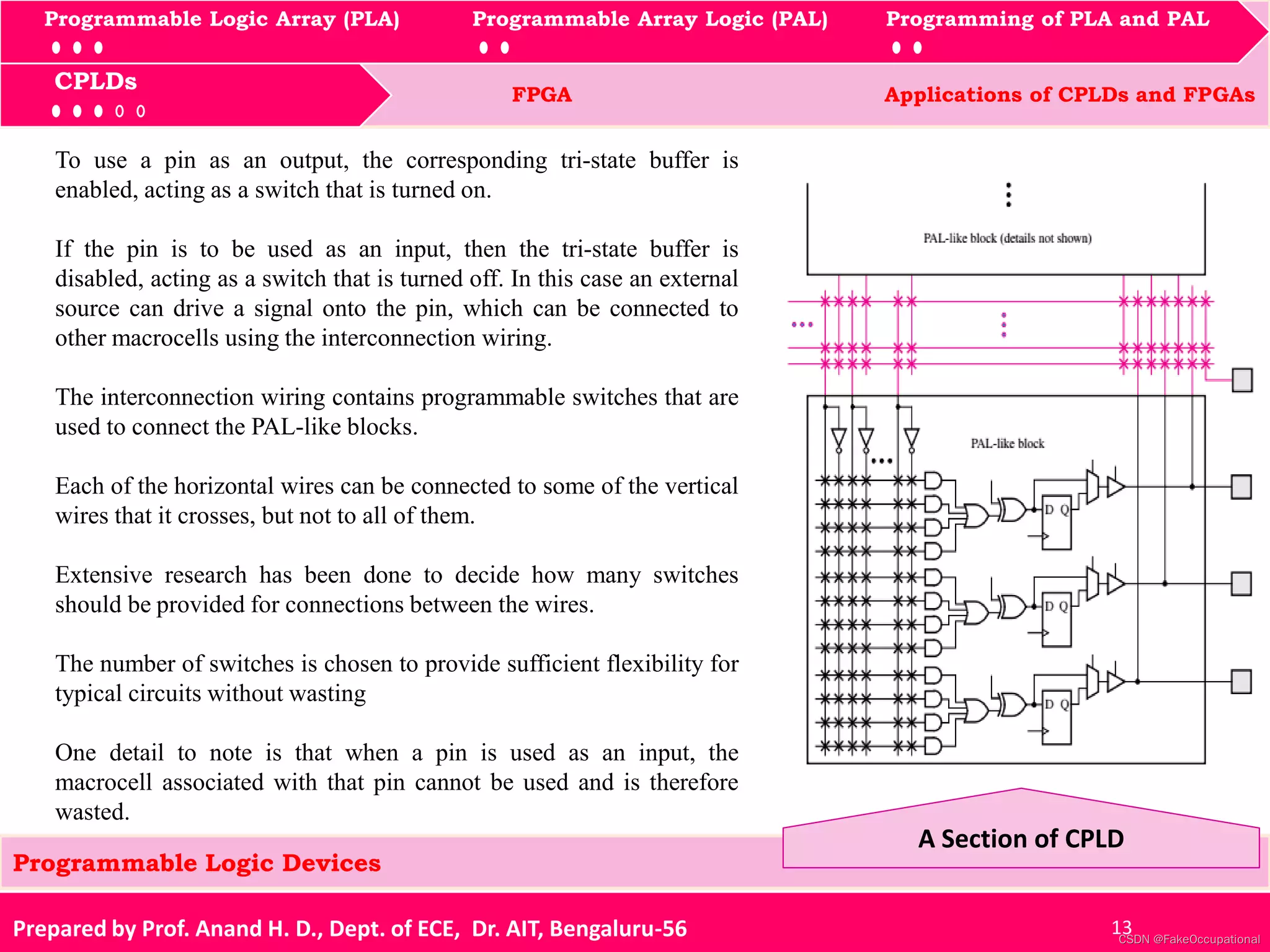

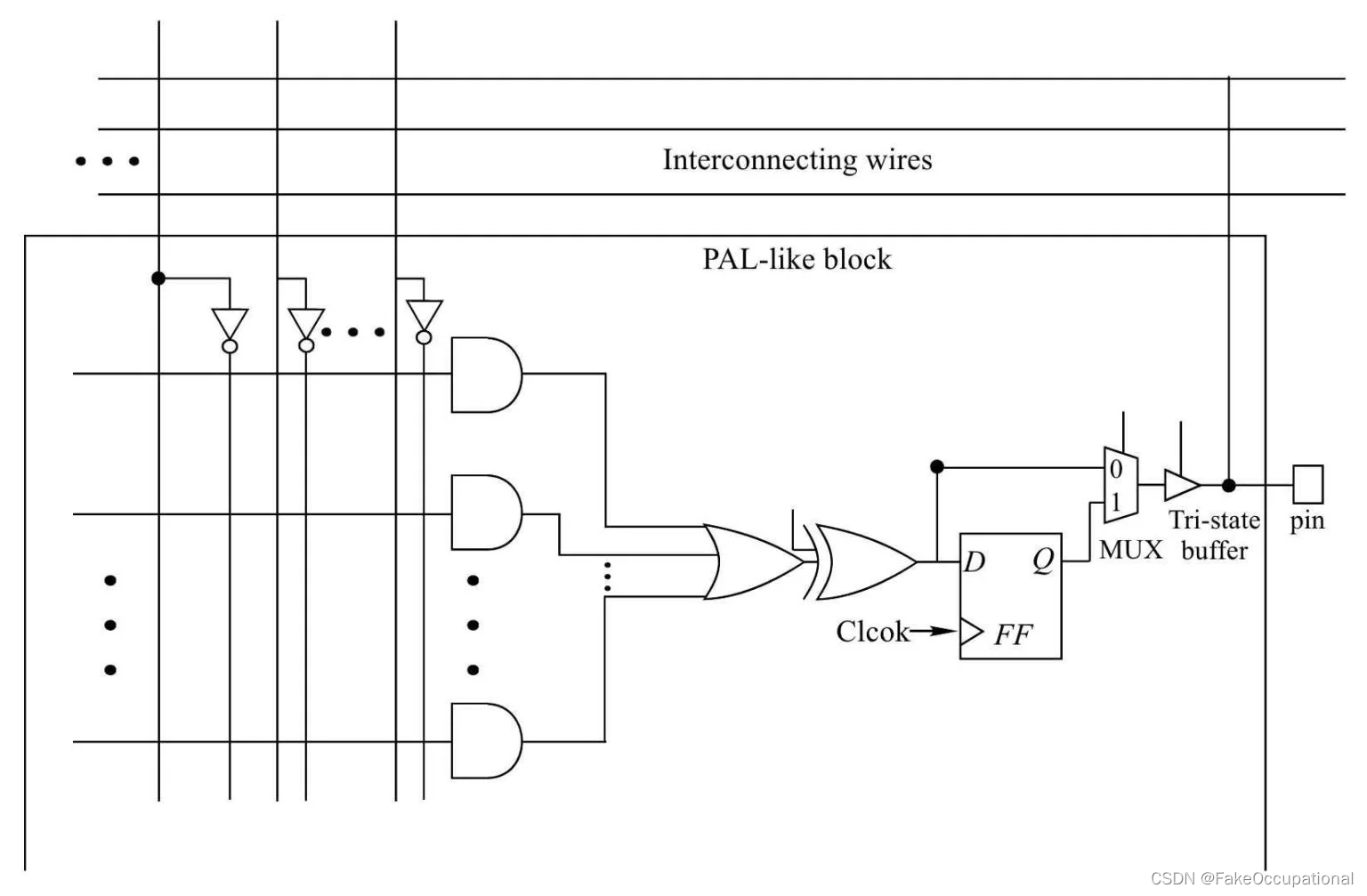

CPLD(Complex Programmable Logic Device)

示例

CPLD 的架构

可编程逻辑块(PLB)

- 存储配置数据的EEPROM,用于设置逻辑块和互连的功能。

- 类PAL块(也称为功能块)通常由16个宏单元组成。每个宏单元由一个与或配置、一个异或门、一个触发器、一个多路复用器和一个三态缓冲器组成。

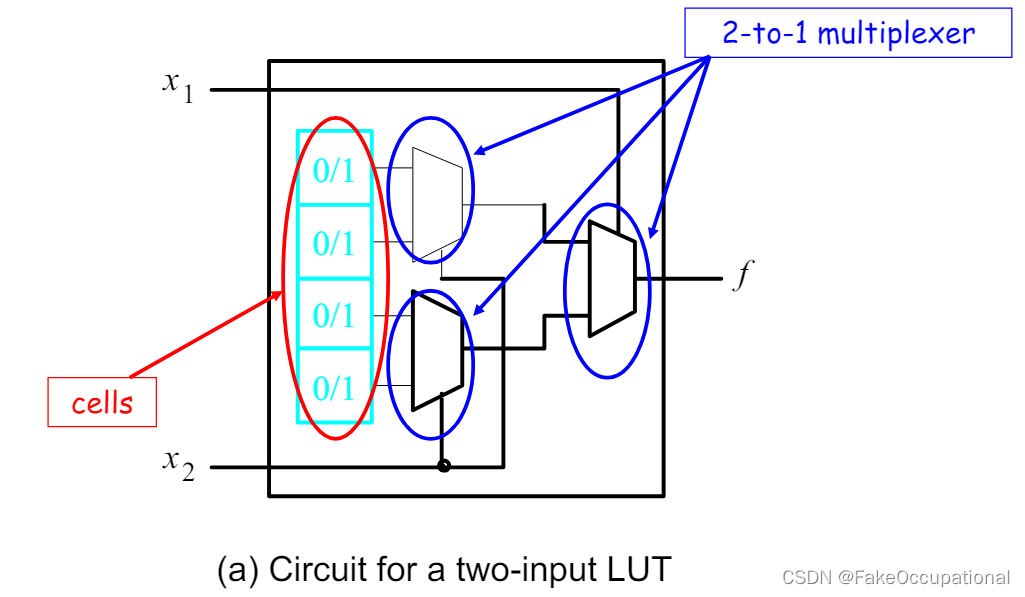

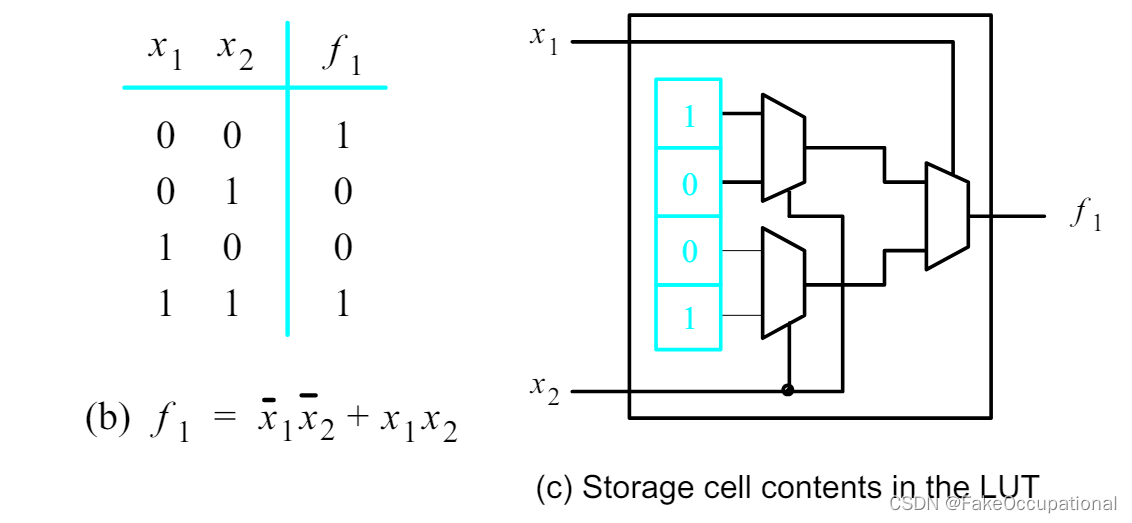

LUT

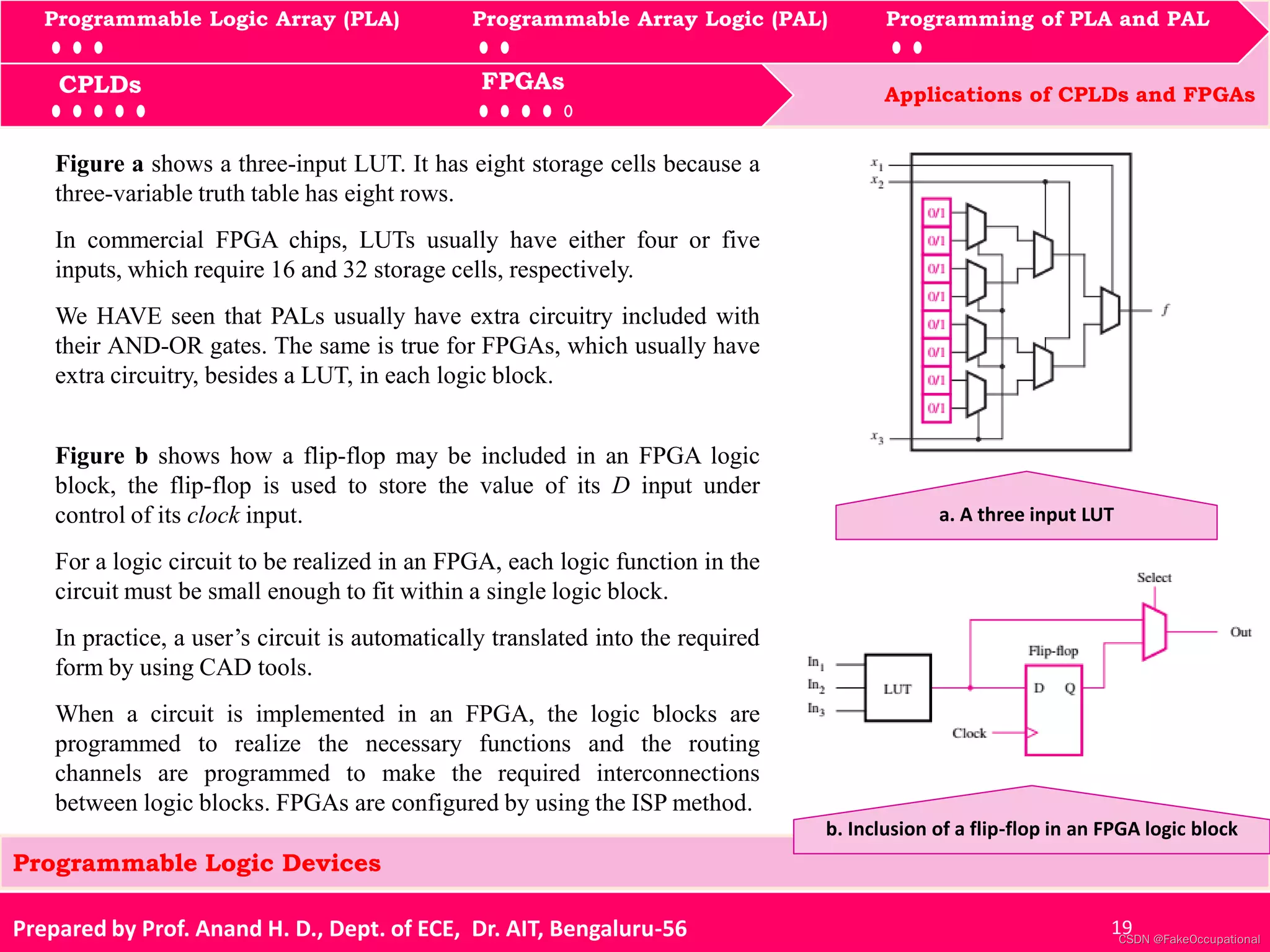

- LUT(Lookup Table,查找表)是数字逻辑设计中常用的一种元件,用于实现逻辑功能。它是一种存储了输入输出关系的数据结构,在电路中充当逻辑函数的实现。LUT的工作原理类似于一张查找表,它接收一组输入信号,并根据这组输入信号查找对应的输出信号。在数字逻辑中,这组输入信号可以是逻辑门的输入,而查找表存储了每一种输入组合对应的输出。例如,对于一个二输入的AND门,有四种可能的输入组合:00、01、10、11。每种输入组合对应一个输出,因此可以用一个包含四个条目的查找表来实现AND门的功能。

- 在商业FPGA芯片中,LUT通常有4个或5个输入,分别需要16个和32个存储单元。

FPGA

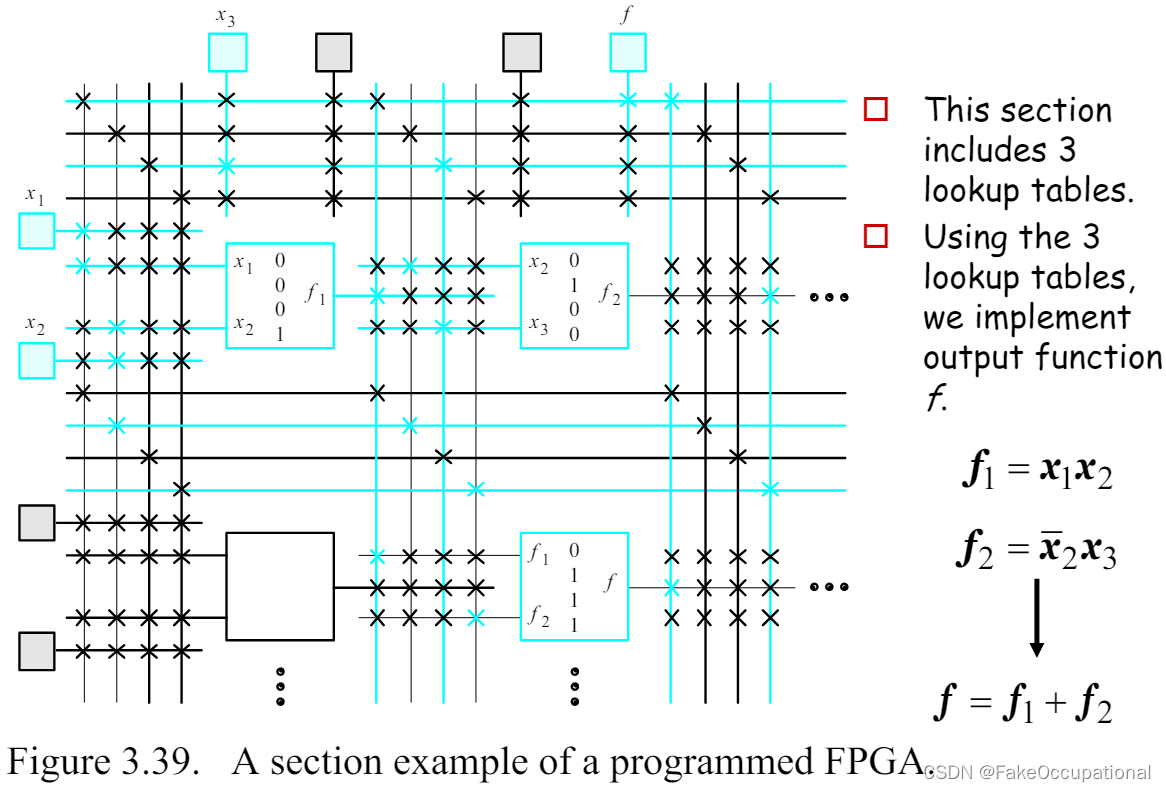

- PAL通常有额外的电路,包括与或门。FPGA也是如此,除了一个LUT之外,它通常在每个逻辑块中有额外的电路。图b显示了一个触发器是如何被包含在FPGA逻辑块中的,触发器被用来在其时钟输入的控制下存储其D输入的值。

- 通过FPGA实现 x 1 x 2 + x 2 ˉ x 3 x_1x_2+\bar{x_2}x_3 x1x2+x2ˉx3:

对比CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)和FPGA(Field-Programmable Gate Array,现场可编程门阵列):

| 特性 | CPLD | FPGA |

|---|---|---|

| 架构 | 由多个宏单元(Macrocell)组成,通过可编程互连网络连接 | 由多个可编程逻辑块(PLB)组成,通过复杂的互连矩阵连接 |

| 配置存储 | EEPROM 或 Flash,断电后保留配置 | 目前,大多数FPGA芯片是基于 SRAM 的结构的,SRAM,断电后配置丢失,需要外部存储加载 |

| 配置时间 | 配置时间较短 | 配置时间较长 |

| 逻辑容量 | 适合中小规模逻辑设计,逻辑容量较低 | 适合大规模、高复杂度逻辑设计,逻辑容量高 |

| 功耗 | 通常较低,适合低功耗应用 | 相对较高,特别是在实现复杂设计时 |

| 时序特性 | 时序特性稳定确定 | 灵活,但时序特性可能受复杂互连影响 |

| 开发工具 | 简单,适合快速原型设计 | 复杂,提供高级特性和调试环境 |

| 编程接口 | 相对简单 | 复杂,支持高级功能和多种配置方式 |

| 典型应用 | 控制电路、简单状态机、I/O 扩展、接口转换 | 高性能计算、数字信号处理、实时数据处理、高速通信接口 |

| 资源 | 较少的逻辑单元和寄存器 | 丰富的逻辑单元、DSP 块、RAM 块 |

| 并行处理 | 限制较多 | 高度并行处理能力 |

| 灵活性 | 架构固定,灵活性较低 | 架构灵活,可重配置 |

CG

- https://en.wikipedia.org/wiki/Programmable_Array_Logic

- https://ja.wikipedia.org/wiki/EPROM

- https://en.wikipedia.org/wiki/EEPROM

- https://www.slideshare.net/anandhd1/programmable-logic-devices-236575565

- https://electronicsforyou.in/cpld/

- https://people.engr.tamu.edu/xizhang/ECEN248/slides_Chapter3_6.pdf

- 可编程只读存储器 PROM 最初是 1956 年作为与洲际弹道导弹相关的军事计划的一部分开发的。这项发明归功于当时在美国博世武器公司工作的 Wen Tsing Chow。商业设备于 1960 年代末问世。

- 1989 年,英特尔在其可训练的人工神经网络 (ETANN) 芯片中采用了 FGMOS 作为模拟非易失性存储器元件,[3] 展示了将 FGMOS 设备用于数字存储器以外的应用的潜力。