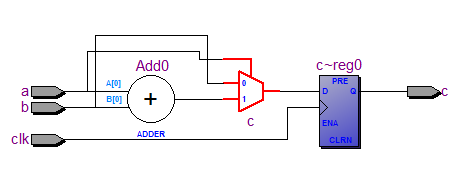

1always块中if的条件内的量可以是变量,也可以是常量parameter

(1)是输入变量时,那么综合出来会有一个选择器

module QQ(a,b,c,clk);

input a,b,clk;

parameter d=1;

output reg c;

always@(posedge clk)

if(a==1) c=a+b;

else c=b;

endmodule

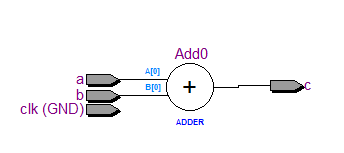

(2)是常量时,会直接综合掉

module QQ(a,b,c,clk);

input a,b,clk;

parameter d=1;

output reg c;

always@(posedge clk)

if(d==0) c=a+b;

else c=b;

endmodule

2generate if内量只能是parameter类型

(1)是变量时会报错

module QQ(a,b,c,clk);

input a,b,clk;

parameter d=1;

output c;

generate

if(a==1) assign c=a+b;

else assign c=c;

endgenerate

endmodule

报错

Error (10734): Verilog HDL error at QQ.v(7): a is not a constant

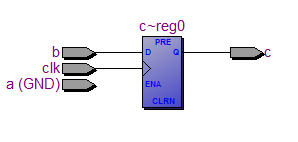

(2)是parameter类型时可以,当然条件选择会直接综合掉

ps:generate中赋值还得assign或者always,再加上条件选择会综合掉,所以generate的作用只是帮助设计者思维设计这么一个过程,不会在设计电路中有体现

module QQ(a,b,c,clk);

input a,b,clk;

parameter d=1;

output c;

generate

if(d==1) assign c=a+b;

else assign c=c;

endgenerate

endmodule