一、单指令周期

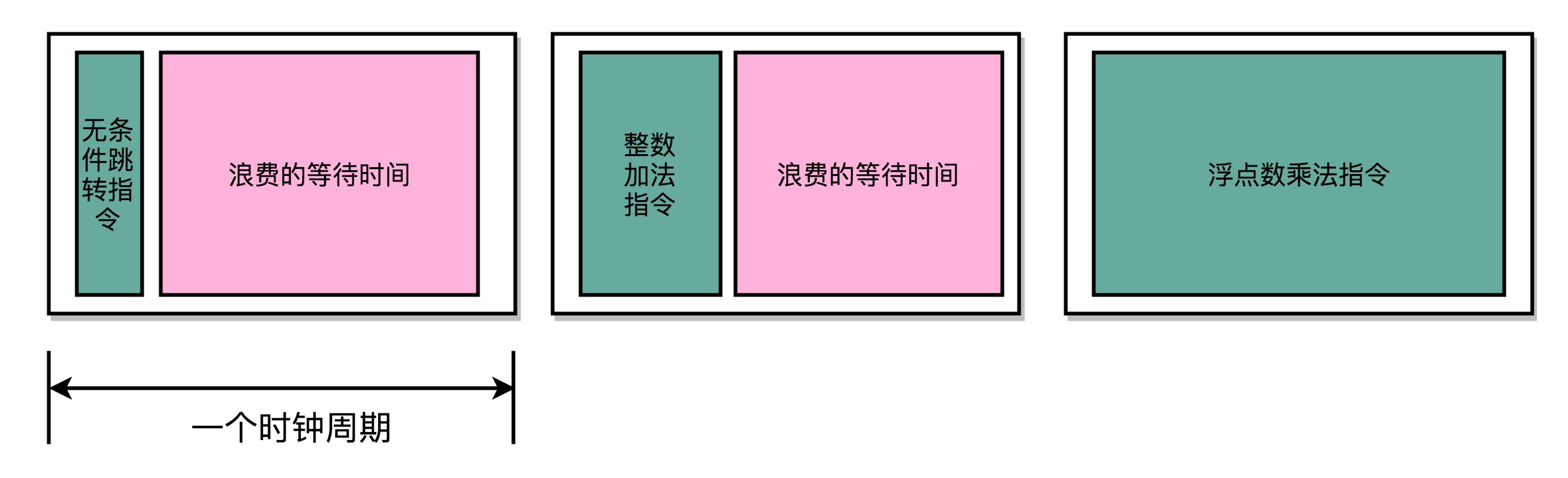

由前可知,一条CPU指令的执行有三个步骤:指令读取、指令译码、指令执行。由于这个过程受CPU时钟的控制,如果我们将这个过程安排在一个CPU时钟周期内执行,这种设计思路就叫单指令周期处理器。这样的设计需要将指令周期时间设为与耗时最长的那条指令执行时间相当,这样显然会使得CPU频率比较,会造成一些简单执行时大量CPU时间被浪费,如图示:

基于这种情况,现代的CPU都不是单指令周期处理器,而是采用了一种指令流水线的技术。

二、现代处理器流水线设计

由于指令的执行一般都可以拆分为多个小步骤,因此我们可以将一个指令的执行分解为诸如“取指令”、“译码”、“执行”这样的散步也可以拆分成更加细的步骤,那么在一个指令的取指令结束之后,可以马上进行下一个指令的取指令操作,如此整个执行效率就可以提高,只要是不存在前后依赖的子指令,理论上都可以并行提高效率。这样一来我们可以把CPU周期时钟周期时间设为一个个小步骤执行的时间即可。这样的协作模式就称为指令流水线,里面每一个独立的步骤就称为流水线阶段或流水线级。这样我们只需保证一个最复杂的流水线操作在一个CPU时钟周期之内完成就好了。

一个指令可以拆分为几个流水线级就称为几级流水线。

理想情况下,将CPU指令拆分成耗时差不多的流水线级是浪费时间最少的方案。在CPU内部也就像一个工厂一样,不同分工的组建不断的处理上游传递下来的内容,而无需等待上一个产品生产完成后再启动下一个商品的生产。

三、超长流水线的性能瓶颈

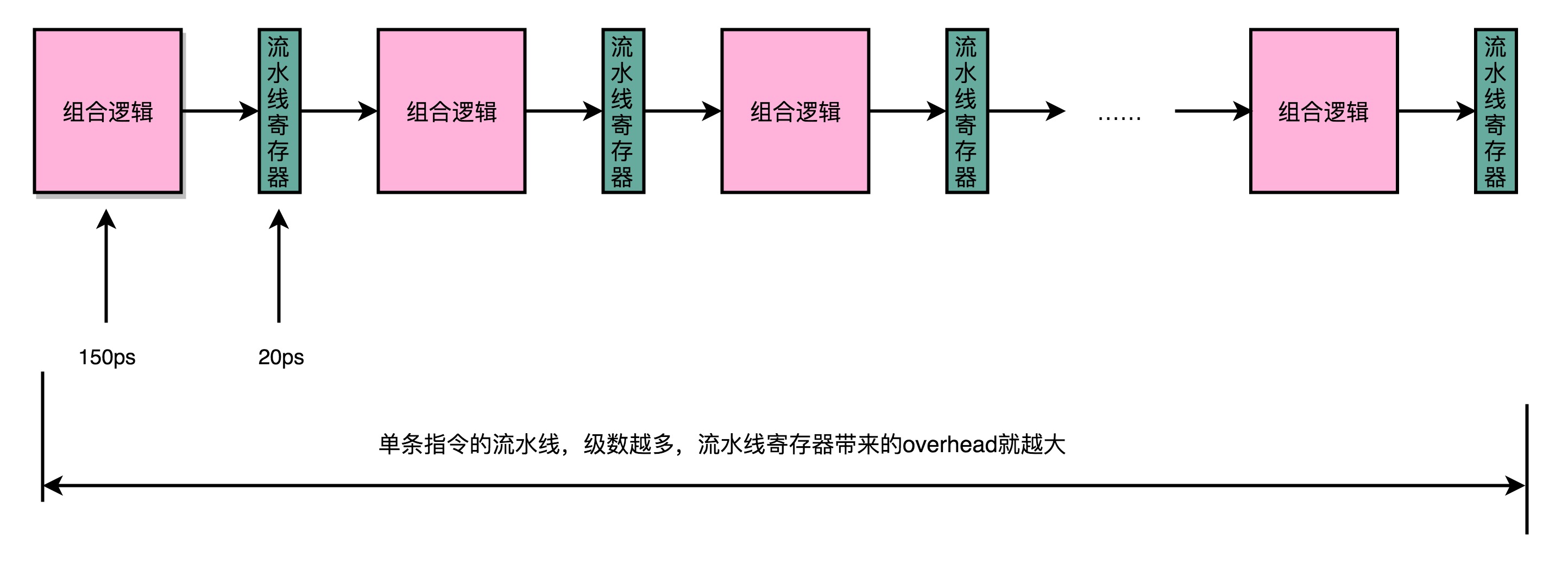

理论上,流水线级数拆分越深,CPU吞吐率会越高,但增加流水线深度也是有成本的,多增加一级流水线就要多一次写入流水线寄存器的操作,如图:

当流水线级数多到一定程度,额外的消耗甚至会大于执行指令的耗时。因此,设计合理的指令流水线级数在现代CPU中是非常重要的。

四、主频战争带来的超长流水线

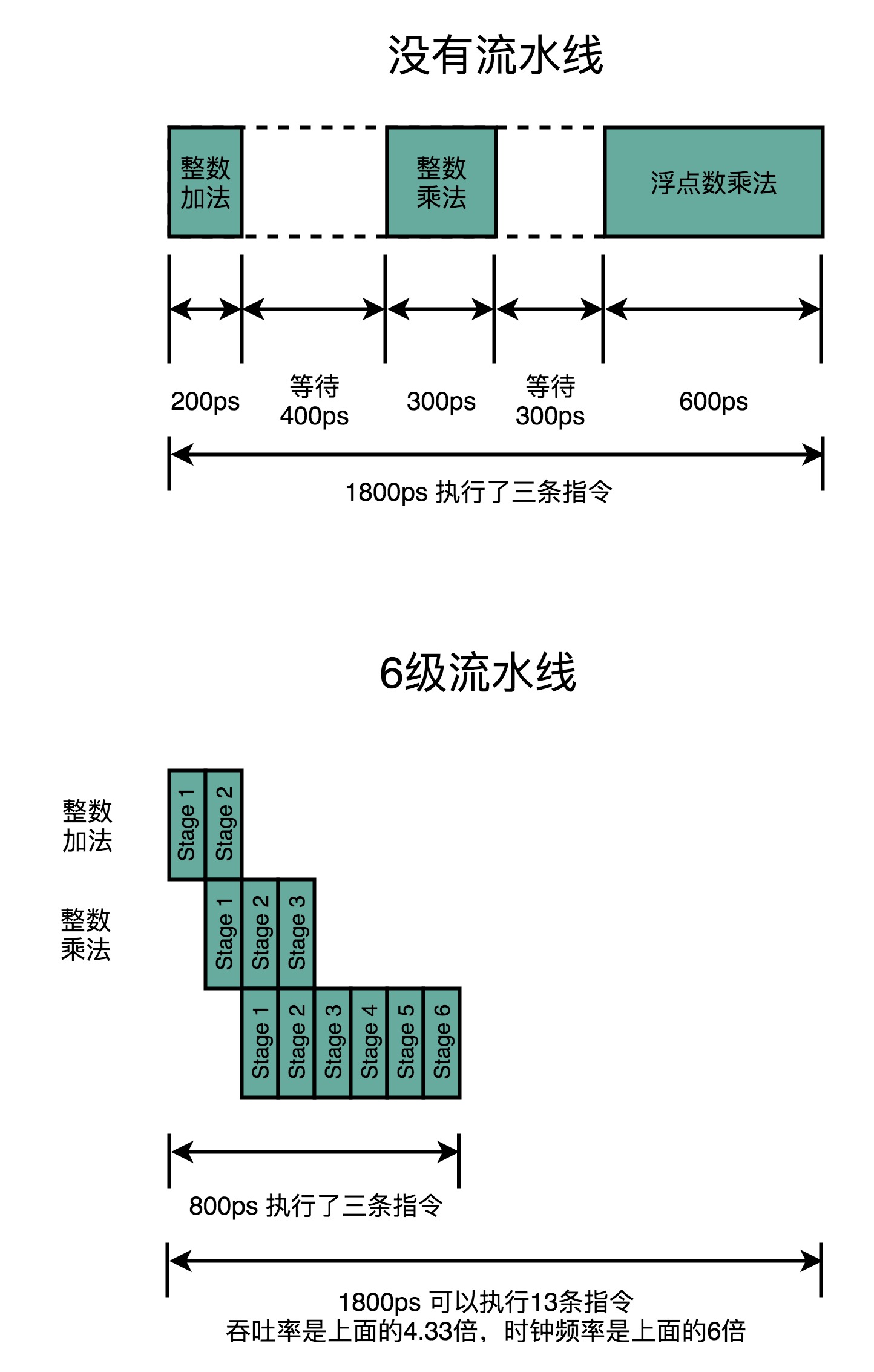

流水线技术并不能减少单条指令的执行时间,只是能够提高运行很多条指令时的吞吐率。举例如下:

- 一条整数加法需要200ps;

- 一条整数乘法需要300ps;

- 一条浮点数乘法需要600ps;

那么在单指令周期情况下,CPU时钟周期应该设为600ps,结果是在1800ps内执行了3条指令。而如果使用六级流水线,每一级流水线都只需要100ps,那么当第一条指令的第一个stage结束之后,第二个指令的第一个stage就开始执行,第二个指令的第一个stage执行完成后,第三个指令就开始执行,这样三条指令的执行总共耗时800ps,吞吐量上升一倍多。

五、新挑战:冒险和分支预测

超长流水线技术至少包含以下几个方面的问题:

- 功耗问题:由于流水线的加深,电路增加、所需要的晶体管增加了很多,使得功耗和散热问题都极为严重。

- 流水线带来的性能提升是理论上的,实际程序执行中,受限于前后步骤的依赖关系,并不一定能够做到;

第二个依赖问题,就是计算机组成里所说的冒险问题,有数据冒险、结构冒险、控制冒险等依赖问题,总体上流水线越长,要解决的依赖问题越严重。应对这些问题的方案有乱序执行、分支预测等,在后面将逐步展开。