Verilog中不同位宽的无符号数和有符号之间赋值的截断和扩展问题

可以直接看结论。。。

长位宽赋值给短位宽的截断问题

unsigned=unsigned

代码如下

二进制结果如下:

按照无符号数解释出来的十进制结果如下:

unsigned=signed

代码如下:

二进制结果如下:

按照无符号数解释出来的十进制结果如下:

signed=unsigned

代码如下:

二进制结果如下:

按照有符号数2的补码解释出来的结果如下:

signed=signed

代码如下:

二进制结果如下:

按照有符号数2的补码解释出来的结果如下:

结论

对于长位宽赋值给短位宽的情况,无论左操作数、右操作数是有符号数还是无符号数,都是直接截断高位,而左操作数二进制所表示的实际十进制数据要看左操作数是无符号数还是有符号数,如果左操作数是无符号数,直接转换成十进制即可,如果是有符号数,则看成2的补码解释成十进制数,这也是实际计算机系统中有符号数的表示方法。

短位宽赋值给长位宽的扩展问题

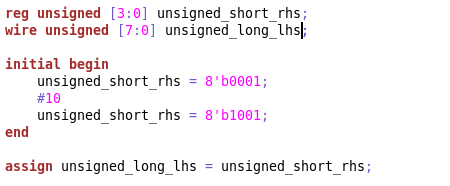

unsigned=unsigned

代码如下:

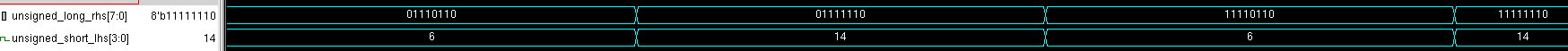

二进制结果如下:

按照无符号数解释出来的结果如下:

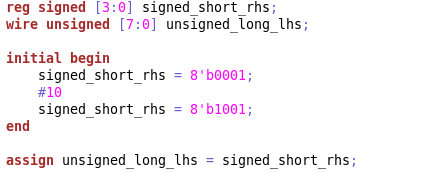

unsigned=signed

代码如下:

二进制结果如下:

按照无符号数解释出来的结果如下:

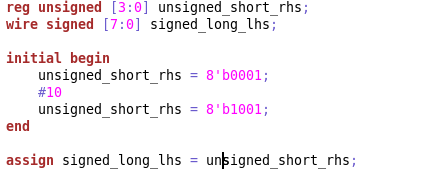

signed=unsigned

代码如下:

二进制结果如下:

按照有符号数2的补码解释出来的结果如下:

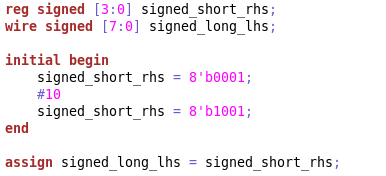

signed=signed

代码如下:

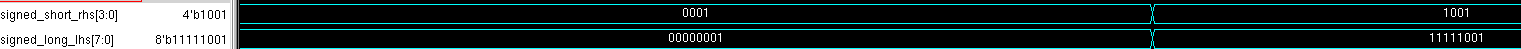

二进制结果如下:

按照有符号数2的补码解释出来的结果如下:

结论

对于短位宽赋值给长位宽的情况,需要对高位进行位扩展,具体是扩展1还是扩展0,记住:完全依据右操作数!,具体如下:

1)右操作数是无符号数,则无论左操作数是什么类型,高位都扩展成0;

2)右操作数是有符号数,则要看右操作数的符号位,按照右操作数的符号位扩展,符号位是1就扩展1,是0就扩展0;

3)位扩展后的左操作按照是无符号数还是有符号数解释成对应的十进制数值,如果是无符号数,则直接转换成十进制数值,如果是有符号数,则看成2的补码解释成十进制数;

4)从上面4种情况看出,有符号数赋值成无符号数会出现数据错误的情况,因此要避免这种赋值,而其他情况都是可以保证数据正确的。

关于无符号和有符号运算的补充

运算和赋值是分开进行的,所以这两个过程可以分开对待,关于赋值的方式上面已经说过,

而运算只要记住一条:

只有RHS中含有无符号数,就按照无符号数的方式运算!