写在前面

整理一些简单的根据时序图编写Verilog代码的实例,帮助新手学习,老手巩固。每次更新两题,根据难度会挑选一些进行讲解。

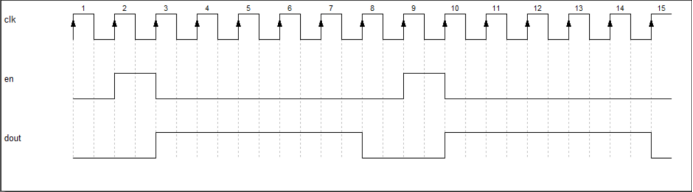

题目 01

题目 01 答案

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 0;

end

else if(add_cnt)begin

if(end_cnt)

cnt <= 0;

else

cnt <= cnt + 1;

end

end

assign add_cnt = dout == 1;

assign end_cnt = add_cnt && cnt== 5-1;

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

dout<= 0;

end

else if(en==1)begin

dout<= 1;

end

else if(end_cnt==1)begin

dout<= 0;

end

end

题目 02

题目 02 答案

本题和01类似,只不过需要切换计数器的时间

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 0;

end

else if(add_cnt)begin

if(end_cnt)

cnt <= 0;

else

cnt <= cnt + 1;

end

end

assign add_cnt = dout == 1;

assign end_cnt = add_cnt && cnt== x-1;

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

dout<= 0;

end

else if(en1==1||en2==1)begin

dout<= 1;

end

else if(end_cnt==1)begin

dout<= 0;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

x<=0;

end

else if (en1==1)begin

x<=2;

end

else if(en2==1)begin

x<=4;

end

end