写在前面

承接本系列上文。整理一些简单的根据时序图编写Verilog代码的实例,帮助新手学习,老手巩固。每次更新两题,根据难度会挑选一些进行讲解。

题目05

题目05答案

这个题的思路挺像02和03(或者04)结合

wire add_cnt;

wire end_cnt;

reg [ :0] cnt ;

assign add_cnt = flag ==1;

assign end_cnt = add_cnt && cnt== x-1;

assign high_flag = add_cnt && cnt== y-1;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 0;

end

else if(add_cnt)begin

if(end_cnt)

cnt <= 0;

else

cnt <= cnt + 1;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

flag <=0;

end

else if(en1==1||en2==1)begin

flag <=1;

end

else if(end_cnt==1)begin

flag <=0

end

else begin

flag <=flag;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

dout<= 0;

end

else if(high_flag==1)begin

dout<= 1;

end

else if(end_cnt==1)begin

dout<= 0;

end

end

always @(*)begin

if(rst_n==1'b0)begin

x=0;

end

else if(en1==1)begin

x=4;

end

else if(en2==1)begin

x=2;

end

else begin

x=x;

end

end

always @(*)begin

if(rst_n==1'b0)begin

y=0;

end

else if(en1==1)begin

y=2;

end

else if(en2==1)begin

y=1;

end

else begin

y=y;

end

end

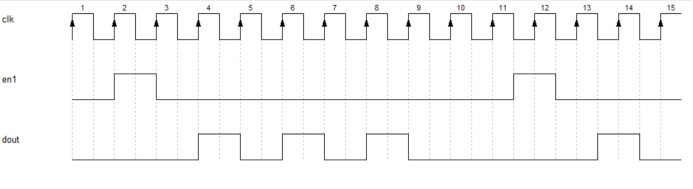

题目06

每次触发后都是第一个波形,三个高电平

题目06答案

佛系更新个可以验证的模块代码,使用的是modelsim。

module

module test06 (

input clk, // Clock

input en1, // Clock Enable

input rst_n, // Asynchronous reset active low

output reg dout

);

wire add_cnt;

wire end_cnt;

reg flag;

reg [3:0] cnt ;

assign add_cnt = flag ==1;

assign end_cnt = add_cnt && cnt== 6-1;

wire high_flag = add_cnt && (cnt== 2-1||cnt== 4-1||cnt== 6-1);

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 0;

end

else if(add_cnt)begin

if(end_cnt)

cnt <= 0;

else

cnt <= cnt + 1;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

flag <=0;

end

else if(en1==1)begin

flag <=1;

end

else if(end_cnt==1)begin

flag <=0;

end

else begin

flag <=flag;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

dout<= 0;

end

else if(high_flag==1)begin

dout<= 1;

end

else if(end_cnt==1)begin

dout<= 0;

end

else begin

dout<= 0;

end

end

endmodule

测试激励

`timescale 1ns/1ps

module tb_my_logic;

reg clk,en1,rst_n;

wire dout;

test06 u1(

clk, // Clock

en1, // Clock Enable

rst_n, // Asynchronous reset active low

dout

);

always #10 clk =!clk;

initial begin

clk = 1;

rst_n=0;en1=0;

#100;

rst_n=1;

#20 en1=1;

#20 en1=0;

end

endmodule

do文件

vlib work

vmap work

vlog "test06.v"

vlog "tb_my_logic.v"

vsim -voptargs=+acc -novopt work.tb_my_logic

add wave /tb_my_logic/*

run -all

仿真截图

验证波形一致。