1.英特尔®Cyclone®IV E设备家族引脚连接准则

1.1 Clock and PLL Pins

1.2 Configuration/ JTAG Pins

1.3 Differential I/O Pins

1.4 External Memory Interface Pins

1.5 Reference Pins

1.6 Supply Pins (See Notes 16 and 17)

2.注释:

1.在Cyclone IV GX器件中,EP4CGX30的器件封装F484和EP4CGX50,EP4CGX75,EP4CGX110和EP4CGX150器件的所有器件封装均支持FPP配置。 在Cyclone IV E器件中,除Cyclone IV E的E144封装外,大多数器件都支持FPP配置。

2.如果CLKIN用作收发器refclk,则必须将VCC_CLKIN设置为2.5V。 每个器件密度的VCC_CLKIN电压是不同的。 EP4CGX30和更小密度的存储体3A和8A上具有VCC_CLKIN,支持1.2 V / 1.5 V / 1.8 V / 2.5 V / 3.0 V / 3.3 V电压。 EP4CGX50和更高密度的存储体3A和8A在支持1.2 V / 1.5 V / 1.8 V / 2.5 V / 3.0 V / 3.3 V电压的情况下具有VCC_CLKIN,而在存储体3B和8B在支持2.5 V的电压中具有VCC_CLKIN。

3.应在考虑要去耦的特定电路的工作频率上提供电源所需的电量后,再选择电源去耦电容器的电容值。 电源平面的目标阻抗应根据设备/电源的电流消耗和压降要求来计算。 然后应使用适当数量的电容器去耦电源层。 由于封装安装的“等效串联电感”,板载电容器的去耦不会高于100 MHz。 对于较高频率的去耦,应考虑使用适当的板设计技术,例如具有低电感的平面间电容。 为了帮助进行去耦分析,Altera的“配电网络(PDN)设计工具”是出色的去耦分析工具。 可通过配电网络设计工具获得PDN设计工具。

4.对于交流耦合链路,可以将交流耦合电容器放置在通道的任何位置。 PCI Express协议要求将交流耦合电容器放置在接口的发送器侧,以允许插入和拔出适配器。

5.使用Cyclone IV早期功耗估算器确定VCCINT和其他电源的电流要求。

6.这些电源可以在多个Cyclone IV器件之间共享电源平面。

7.收发器信号GXB_RX [0:7]和GXB_TX [0:7]取决于设备。

8.将单独的电源岛用于VCCA和VCCD_PLL。 PLL电源可能来自板上的另一个平面,但必须使用铁氧体磁珠或其他等效方法进行隔离。 如果使用铁氧体磁珠,请选择0402封装,该封装的直流电阻低,额定电流要大于与其连接的电源(VCCA或VCCD_PLL)的最大稳态电流,并且在100 MHz时具有高阻抗。

9.每个设备密度专用全局时钟的数量是不同的。 请参考《 Cyclone IV器件手册》中的“ Cyclone IV器件中的时钟网络和PLL”一章。

10.对于每种设备密度,由GPLL和MPLL组成的PLL的数量是不同的。 EP4CGX15支持3个PLL。 EP4CGX22和EP4CGX30(F484封装除外)支持4个PLL。 EP4CGX30 F484封装,EP4CGX50和其他更大的Cyclone IV GX密度支持8个PLL。 EP4CE6和EP4CE10支持2个PLL。 EP4CE15和其他更大的Cyclone IV E密度支持4个PLL。

11.VCCH_GXB,VCCA_GXB和VCCA可以使用最大电压波动为±3%的开关稳压器。 VCCD_PLL和VCCL_GXB可以使用电压波动最大为±3%的开关电源。

12.必须按照Quartus II软件设置中的指定连接未使用的引脚。 Quartus II的未使用引脚的默认设置为“使用弱上拉电阻将输入设为三态”,除非对于特定的引脚,Quartus II软件会自动将它们连接至GND。 要更改设置,请转到“分配”,然后转到“设备”。 单击“设备和引脚选项”对话框,然后转到“未使用的引脚”选项卡。 您可以从“保留所有未使用的引脚”下拉列表中选择所需的设置。

13.将Cyclone IV器件与2.5 V / 3.0 V / 3.3 V配置电压标准接口时,必须遵循特定的要求。 所有I / O输入必须保持最大交流电压为4.1V。请参见“ Cyclone IV器件中的配置和远程系统升级”一章的配置和JTAG引脚I / O要求。

14.每个设备密度和封装的差分TX / RX通道是不同的。 请参考《 Cyclone IV器件手册》中的“ Cyclone IV器件中的I / O功能”一章。

15.有关在不同器件密度下支持DQ和DQS总线模式的详细信息,请参见Cyclone IV器件手册中的“ Cyclone IV器件中的外部存储器接口”一章。

16.Altera强烈建议对封装上的每个独立电源或接地球使用独立的PCB通孔。 在PCB上共享电源或接地引脚过孔可能会导致噪声耦合到器件中,并导致抖动性能降低。

17.有关最低电源调节器的建议,请参考下面“电源调节器”选项卡上的示例1和图1。

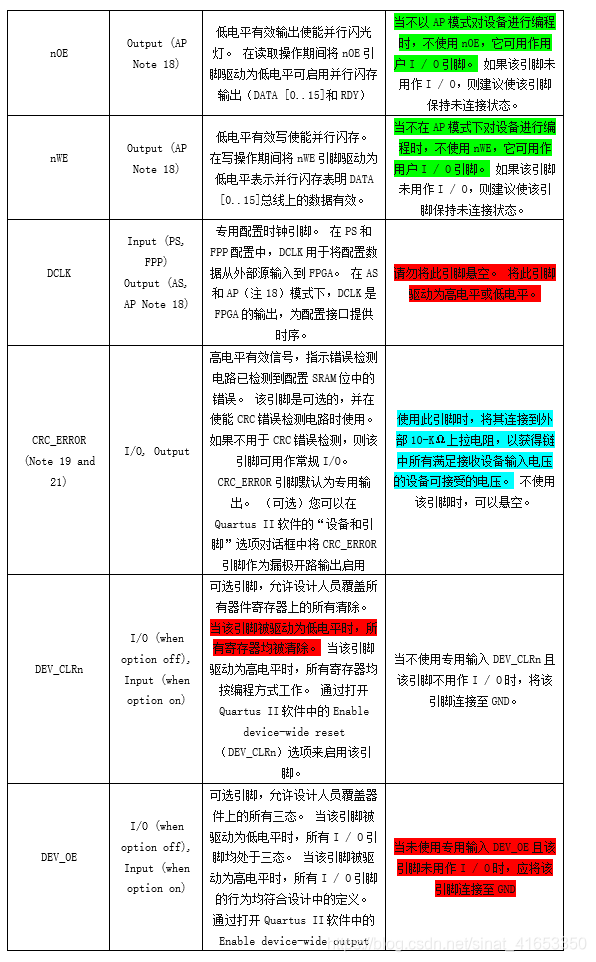

18.仅在Cyclone IV E器件中支持AP模式下的配置,而在Cyclone IV GX器件中不支持。

19.仅在VCCINT 1.2 V的Cyclone IV E器件中支持CRC错误检测,而在VCCINT 1.0 V的Cyclone IV E器件中不支持CRC错误检测。

20.在Quartus II中编译设计项目后创建的Quartus II .pin文件将未使用的收发器或时钟输入引脚列出为GXB_GND (未使用的GXB_RX,REFCLK),GXB_NC(未使用的GXB_TX)和GND +(未使用的输入时钟和PLL)。 验证Quartus II .pin文件中列出的所有引脚均已按照这些建议中的说明连接至开发板上。

21.Cyclone IV E器件有两种变体。 一个由内核电压VCCINT 1.0 V供电,另一个由内核电压VCCINT 1.2 V供电。每个型号都有不同的订购代码。

22.在Cyclone IV GX器件中,每种器件密度的可选高速差分参考时钟输入的数量是不同的。

23.如果Cyclone IV GX器件中没有使用任何收发器,则可以将收发器电源引脚VCCL_GXB,VCCH_GXB和VCCA_GXB连接到GND。 此外,您可以将RREF0引脚直接连接到GND。

24.对于以≥2.97 Gbps运行的收发器应用,请参阅表1。

25.某些Cyclone IV器件封装的底部具有裸露的接地垫。 有关更多信息,请参考Altera器件封装信息数据表的“器件和封装交叉参考”部分。