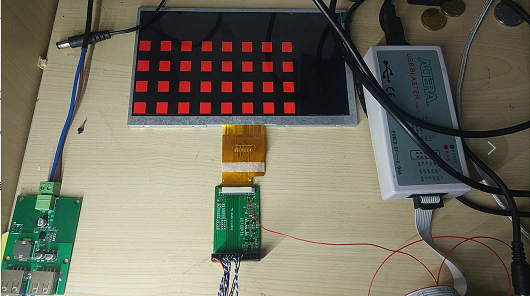

之前一直想试试用Cyclone的LVDS接口驱动屏,第一次尝试时自己做了块小板,当时研究不够深,没有正确的使用Cyclone IV的LVDS接口,这里的正确使用是在Quartus中可以直接分配LVDS类型的IO口,板子做回来后编写Verilog调试时发现Quartus不能给自己用的引脚分配LVDS标准,看了错误报告说可以使用LVDS_E_3R,但是使用了LVDS_E_3R后也不能正常把屏点亮,就这样折腾了一段时间,不断的去看手册,最后才知道自己引出的差分接口全是模拟的LVDS接口,需要加电平匹配电路,报告中推荐使用的LVDS_E_3R,就是使用3个匹配电阻来实现LVDS标准匹配如下图:

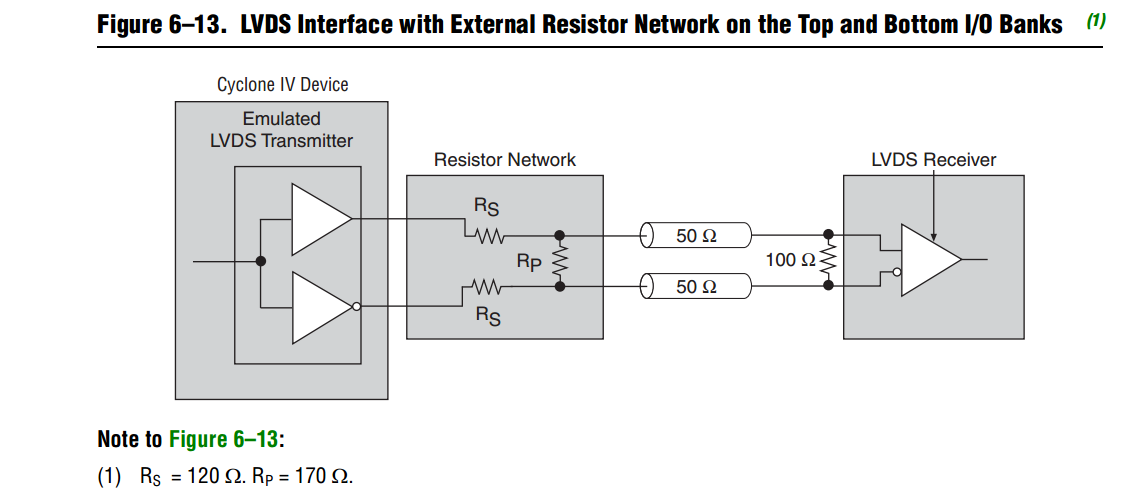

当时根据这点信息把板子的线割掉,在洞洞板上焊了这个匹配电路,然后从板子飞线出来到这个电路上,再飞线回去,重新测试后屏幕有图像显示,只不过一直在抖动,猜猜是飞线导致四对差分対时延过大的问题,然后放置了一段时间没去折腾了。后面在淘宝淘了一块引出来好LVDS接口的板子,又想再尝试用它来点LVDS屏,折腾了几次,也一直没成功,期间一直调LVDS的输出时钟相位,如下:

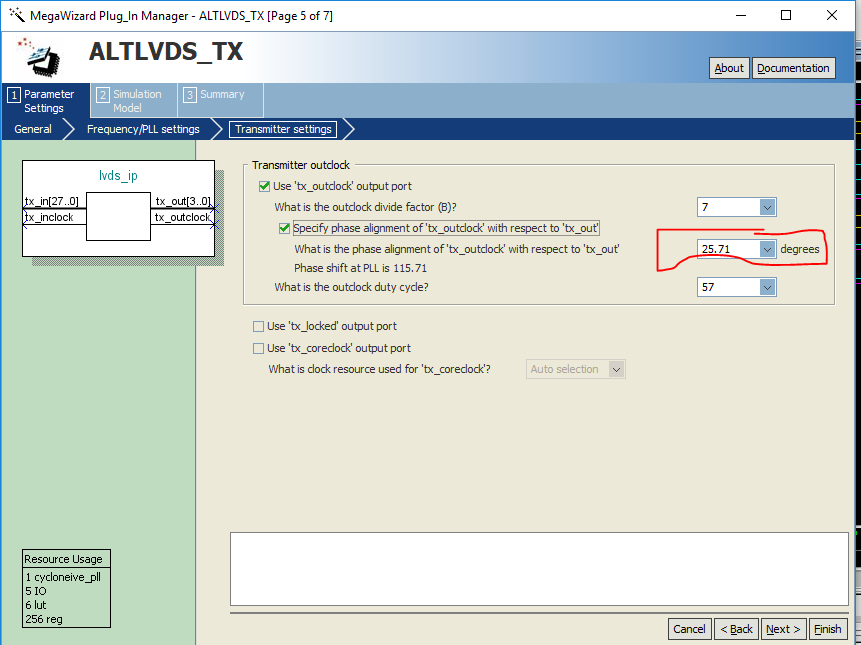

各种尝试也没成功,后面又尝试调节数据与输入时钟对齐相位,如下:经过尝试后发现能解决问题,大概分析是数据锁定时序的问题,跟想象也能对应得上,想尝试通过逻辑仿真验证一下该原因,但是仿真出来的波形无论如何调节都一致,疑问无法得到验证,不过有遇到同样现象的网友也可以做这个调节试试看看能不能解决问题。

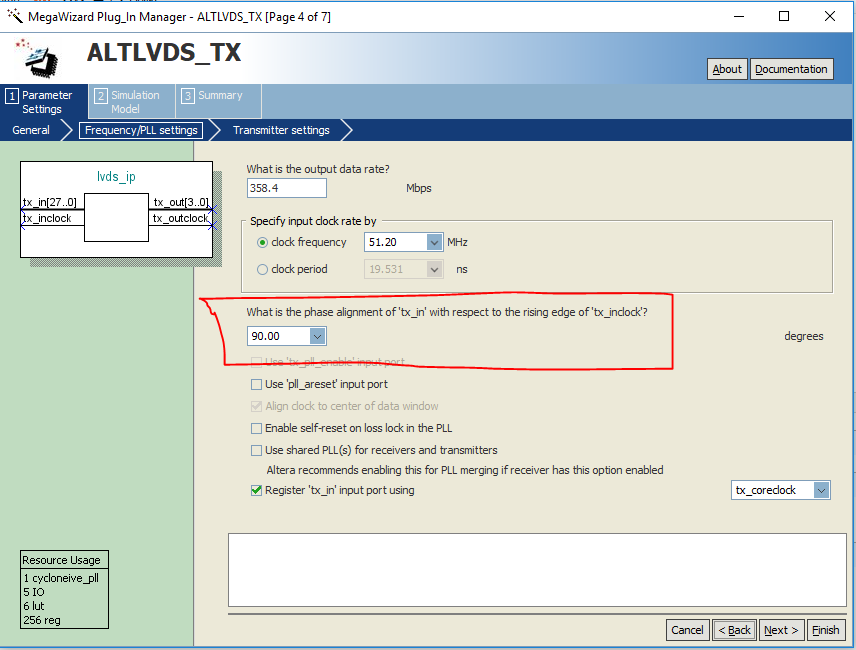

最后献上一张最终结果的图,显示的逻辑块是之前一个800*480分辨率的测试图,懒得改对应到当前的分辨率 ^~^