-

目录

计算机的主存储器(主存(内存))与辅助存储器(辅存(磁盘))

-

计算机的总线

-

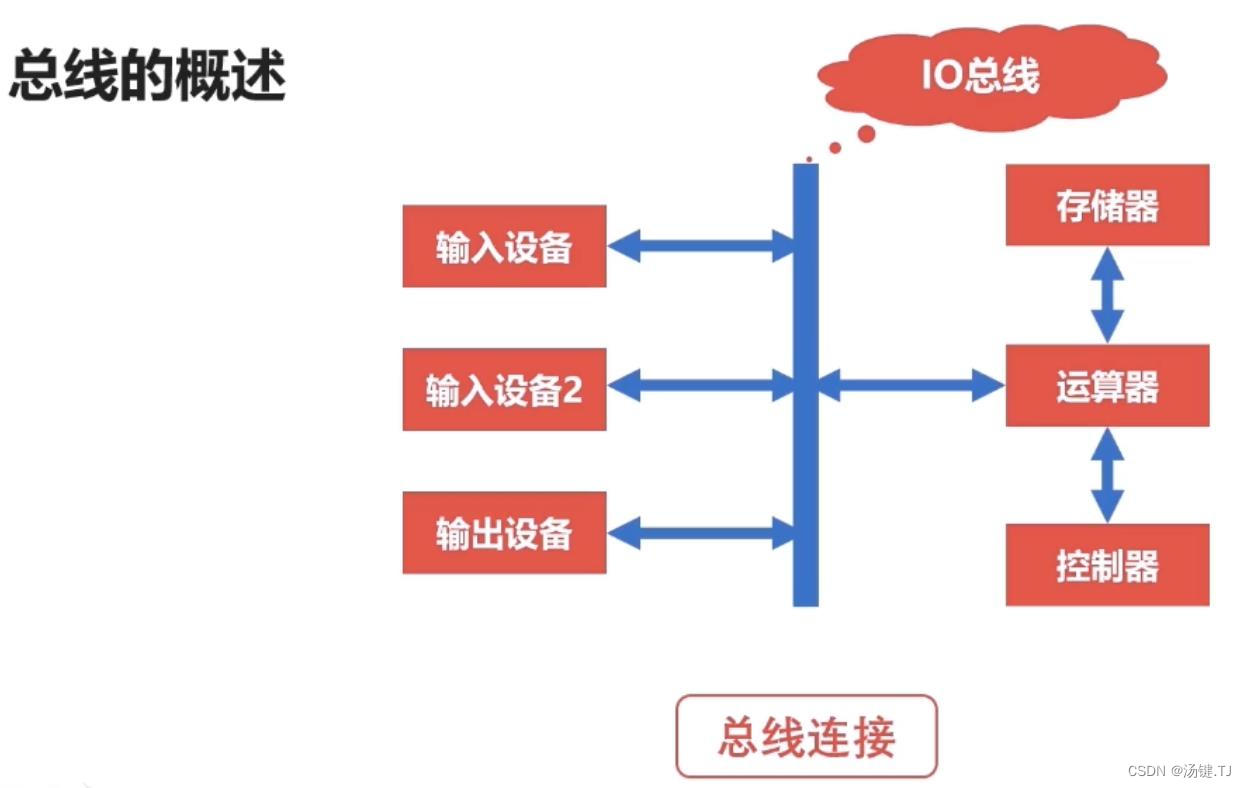

总线的概述

- USB(通用串行总线)

- 提供了对外连接的接口

- 不同设备可以通过USB接口进行连接

- 连接的标准,促使外围设备接口的统一

- 其余常见总线

- PCI总线

- ISA总线

- Thunderbolt总线.....

- 总线就是为了解决不同设备之间的通信问题而存在的

-

总线的分类

- 主要分成2类:分别为片内总线和系统总线

- 片内总线

- 在芯片内部的总线,芯片通过片内总线能简化内部的电路结构

- 就是高集成度芯片内部的信息传输线

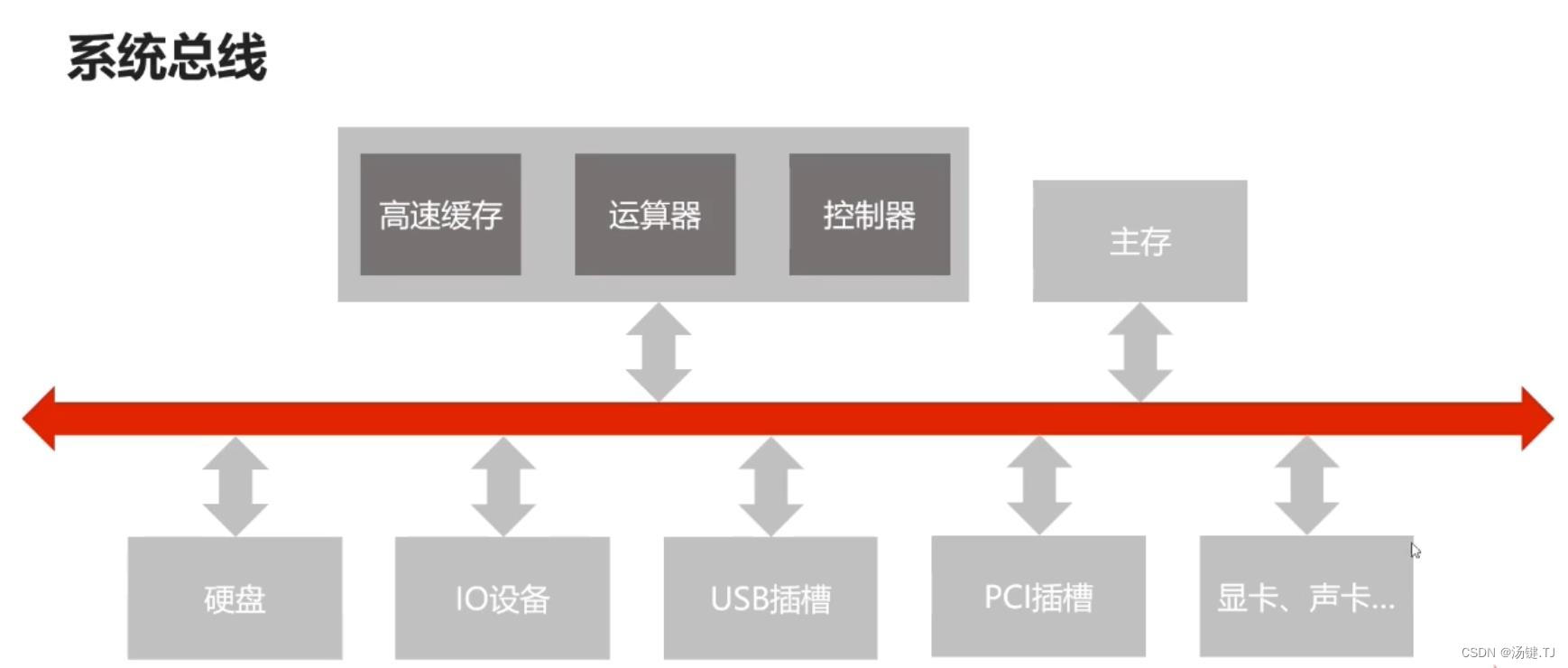

- 系统总线

- USB就是属于系统总线的一种

- 它就是连接计算机外围各种设备的一条总线

- 系统总线总的而言可以分成3类

- 数据总线

- 对于数据总线,总线的位数一般与CPU位数相同(32位,64位)

- 用于双向传输各个部件的数据信息

- 数据总线的位数(总线宽度)是数据总线的重要参数

- 如果说这个总线是32位的话,那么它一次可以传输32位4个字节的数据

- 如果说这个总线是64位的话,那么它一次可以传输64位8个字节的数据

- 地址总线

- 是用于传输数据的地址而使用的,用于寻址

- 地址总线位数=n; 寻址范围:0~2的n次方

- 是指定源数据或目的数据在内存中的地址的一条总线

- 地址总线的位数与存储单元有关

- 控制总线

- 用来发出各种控制信号的传输线

- 控制信号经由控制总线从一个组件发给另外一个组件

- 控制总线可以监视不同组件之间的状态(就绪/未就绪)

-

总线的仲裁

- 为什么需要总线的仲裁

- 假设计算机里面有硬盘和IO设备交换数据,在这时硬盘和IO设备都已就绪,那么总线是由硬盘来使用还是由IO设备来使用呢?如果没有第3方的仲裁器来解决这个矛盾问题的话,那么将引起设备之间的冲突

- 这就是仲裁器存在的理由

- 仲裁器的目的就是解决不同设备使用总线优先顺序的设备即为了解决总线使用权的冲突问题

- 总线仲裁的方法

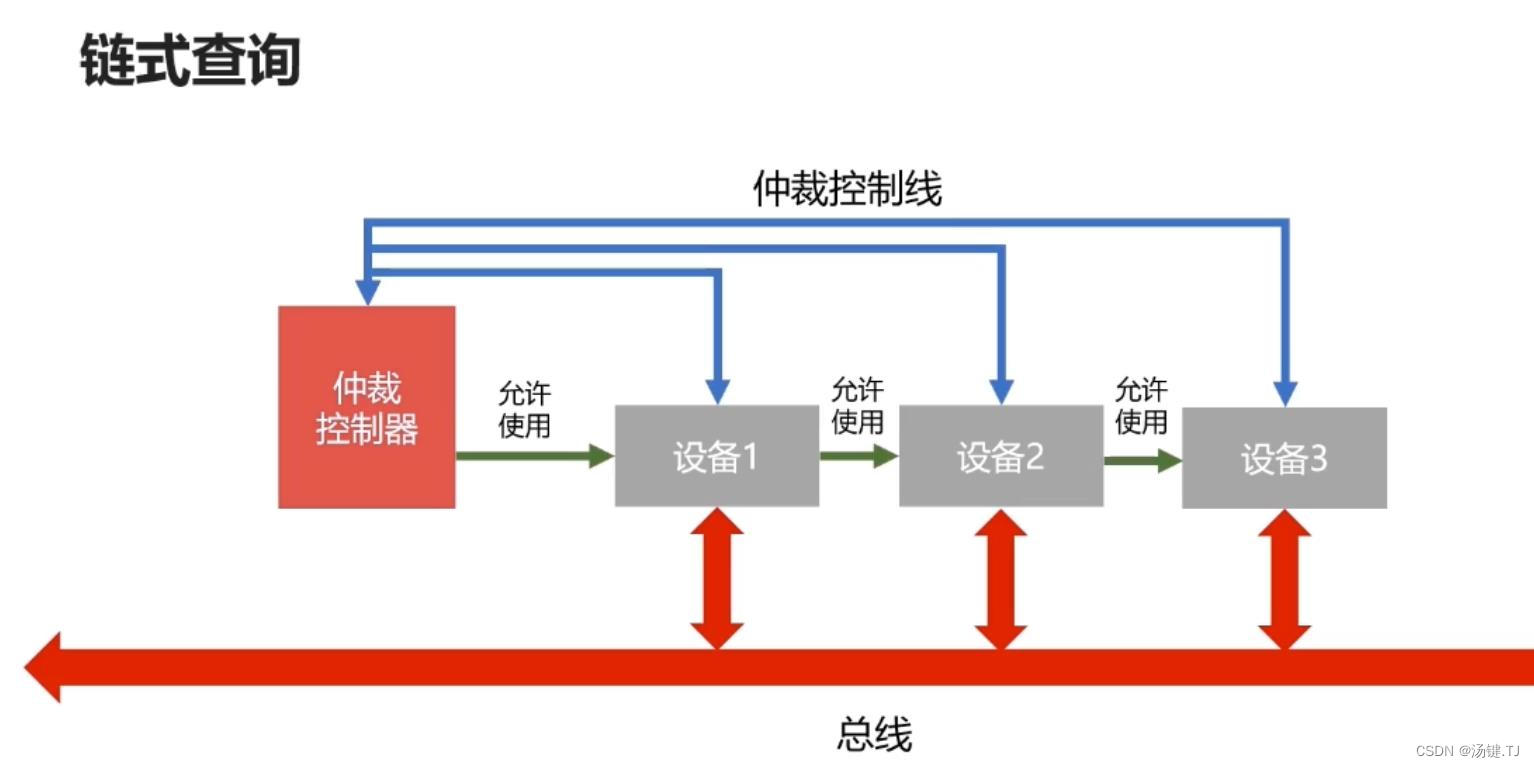

- 链式查询

- 同时请求时,处理顺序如图所示

- 好处:

- 电路复杂度低,仲裁方式简单

- 坏处:

- 优先级低的设备难以获得总线使用权,对电路故障敏感

- 计时器定时查询

- 过程:

- 仲裁控制器对设备编号并使用计数器累计计数

- 控制器接收到仲裁信号后,往所有设备发出计数值

- 计数值与设备编号一致则获得总线使用权

- 独立请求

- 每个设备均有总线独立连接到仲裁器

- 设备可单独向仲裁器发送请求和接收请求

- 当同时收到多个请求信号,仲裁器有权按优先级分配使用权

- 好处:

- 响应速度快,优先顺序可动态改变

- 坏处:

- 设备连接多,总线控制复杂

-

计算机的输入输出设备

- 常见输入设备

- 字符输入设备,图像输入设备

- 字符输入设备

- 键盘:薄膜键盘,机械键盘,电容键盘

- 图像输入设备

- 鼠标,数位板,扫描仪

- 图像输出设备

- 显示器,打印机,投影仪

-

输入输出接口的通用设计

- 接口设计主要有数据线,状态线,命令线,设备选择线

- 数据线

- 是I/O设备与主机之间进行数据交换的传送线

- 分为单向传输数据线和双向传输数据线

- 状态线

- IO设备状态向主机报告的信号线

- 查询设备是否已经正常连接并就绪

- 查询设备是否已经被占用

- 命令线

- CPU向设备发送命令的信号线

- 发送读写信号

- 发送启动停止信号

- 设备选择线

- 主机选择I/O设备进行操作的信号线

- 对连在总线上的设备进行选择

-

CPU与IO设备的通信

- 了解一个情况:CPU速度与IO设备速度不一致

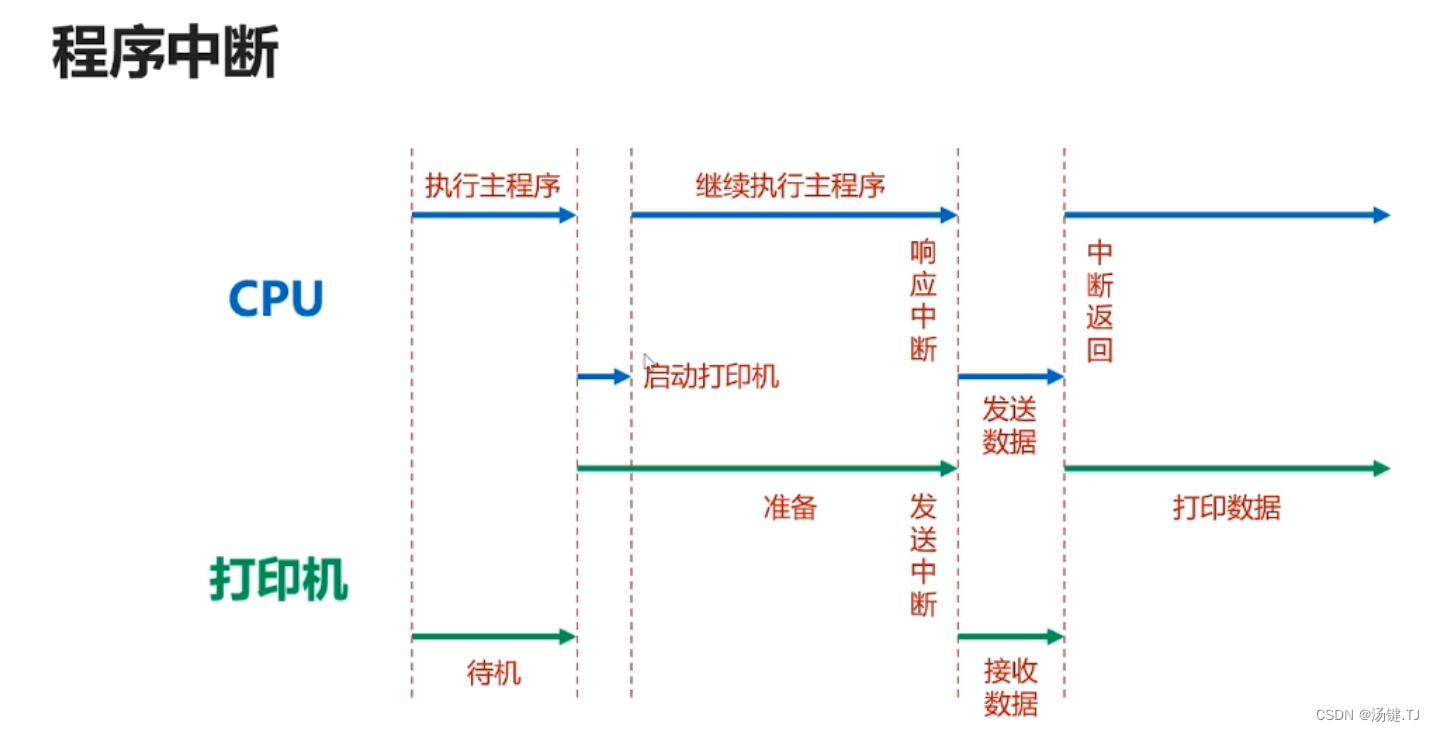

- 程序中断方法

- 当外围IO设备就绪时,向CPU发出中断信号

- CPU有专门的电路响应中断信号

- 简化流程:

- 是提供低速设备通知CPU的一种异步的方式

- 由于有了这个中断,CPU可以高速运转同时兼顾低速设备的响应

- DMA(直接存储器访问)

- DMA直接连接主存与IO设备

- 需要进行通信时,DMA工作时不需要CPU的参与

-

计算机存储器概览

-

存储器的分类

- 按存储介质分类

- 分为半导体存储器,磁存储器

- 内存,U盘,固态硬盘都属于半导体存储器

- 磁带和磁盘属于磁存储器

- 按存取方式分类

- 分为随机存储器(RAM),串行存储器,只读存储器(ROM)

- 随机存储器(RAM):

- 随机读取,与位置无关

- 串行存储器:

- 按顺序查找,与位置有关

- 只读存储器(ROM):

- 只读不写

-

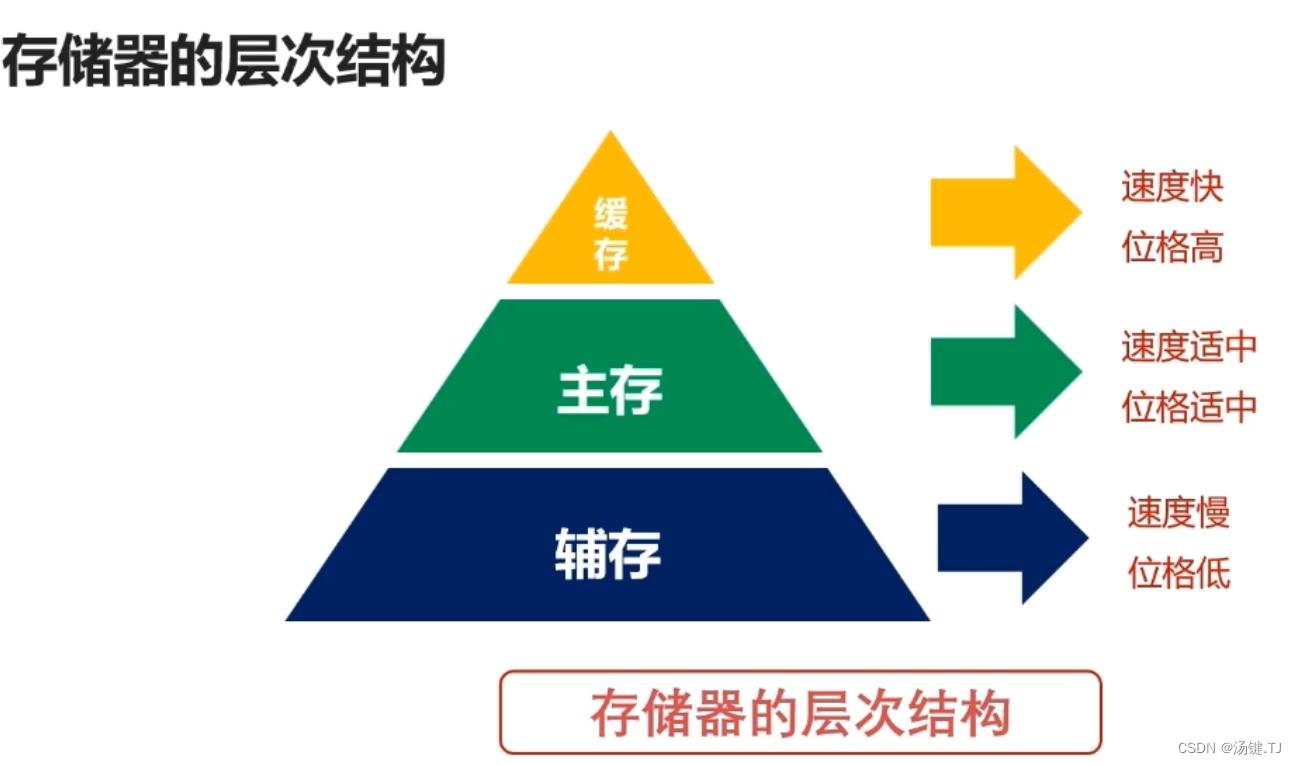

存储器的层次结构

- 存储器考虑因素

- 读写速度

- 存储容量

- 价格

- 容量+价格=>位价:每比特位价格

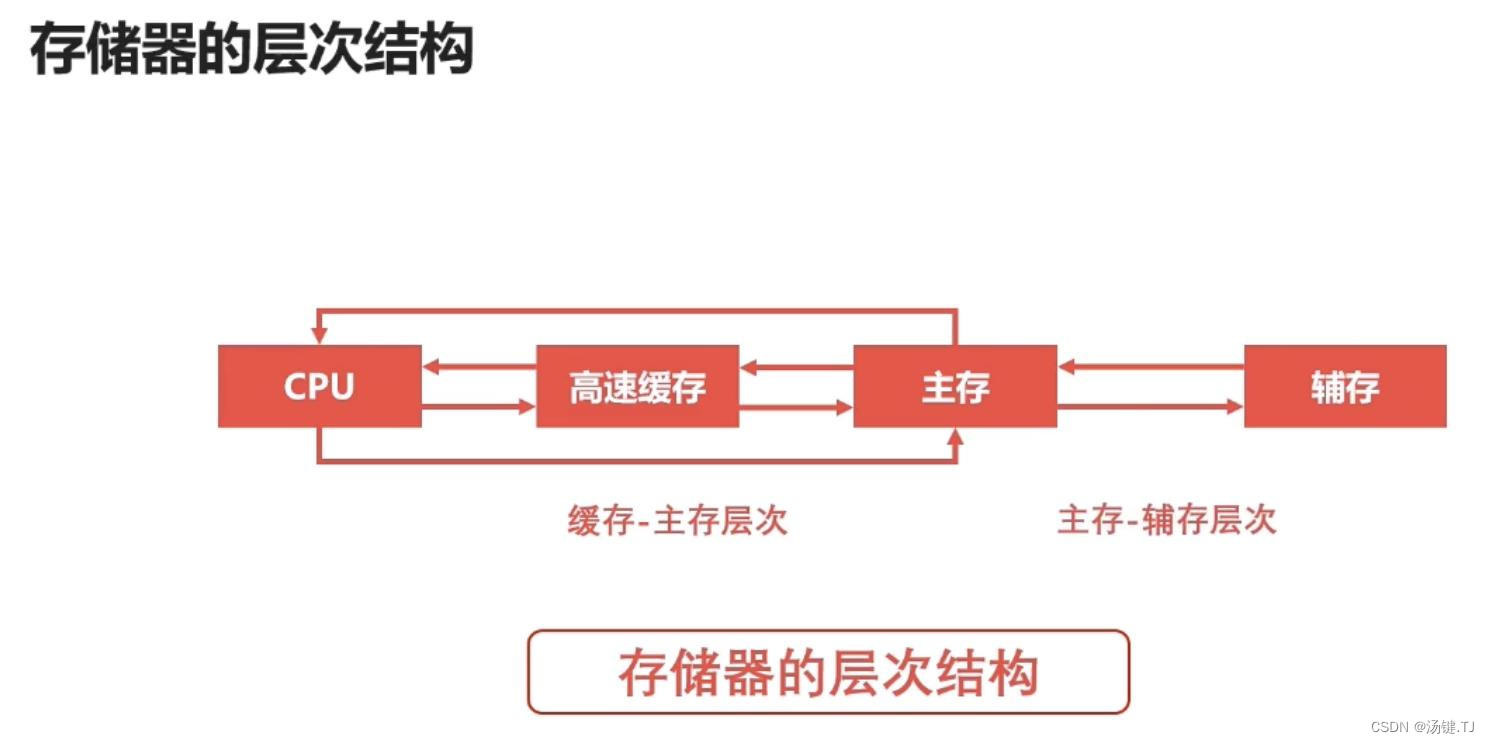

- 对于缓存-主存层次

- 原理:局部性原理

- 实现:在CPU与主存之间增加一层速度快(容量小)的Cache(高速缓存)

- 目的:解决主存速度不足的问题(因为有高速缓存的存在,可以通过一定策略使CPU尽可能访问高速缓存,而不是访问主存,从而提升CPU利用效率和计算机整体运行速度)

- 局部性原理

- 局部性原理是指CPU访问存储器时,无论是存取指令还是存取数据,所访问的存储单元都趋于聚集在一个较小的连续区域中

- 对于主存-辅存层次

- 原理:局部性原理

- 实现:主存之外增加辅助存储器(磁盘,SD卡,U盘等)

- 目的:解决主存容量不足的问题

-

计算机的主存储器(主存(内存))与辅助存储器(辅存(磁盘))

- 为什么计算机断电,内存数据丢失,磁盘数据不会丢失?

-

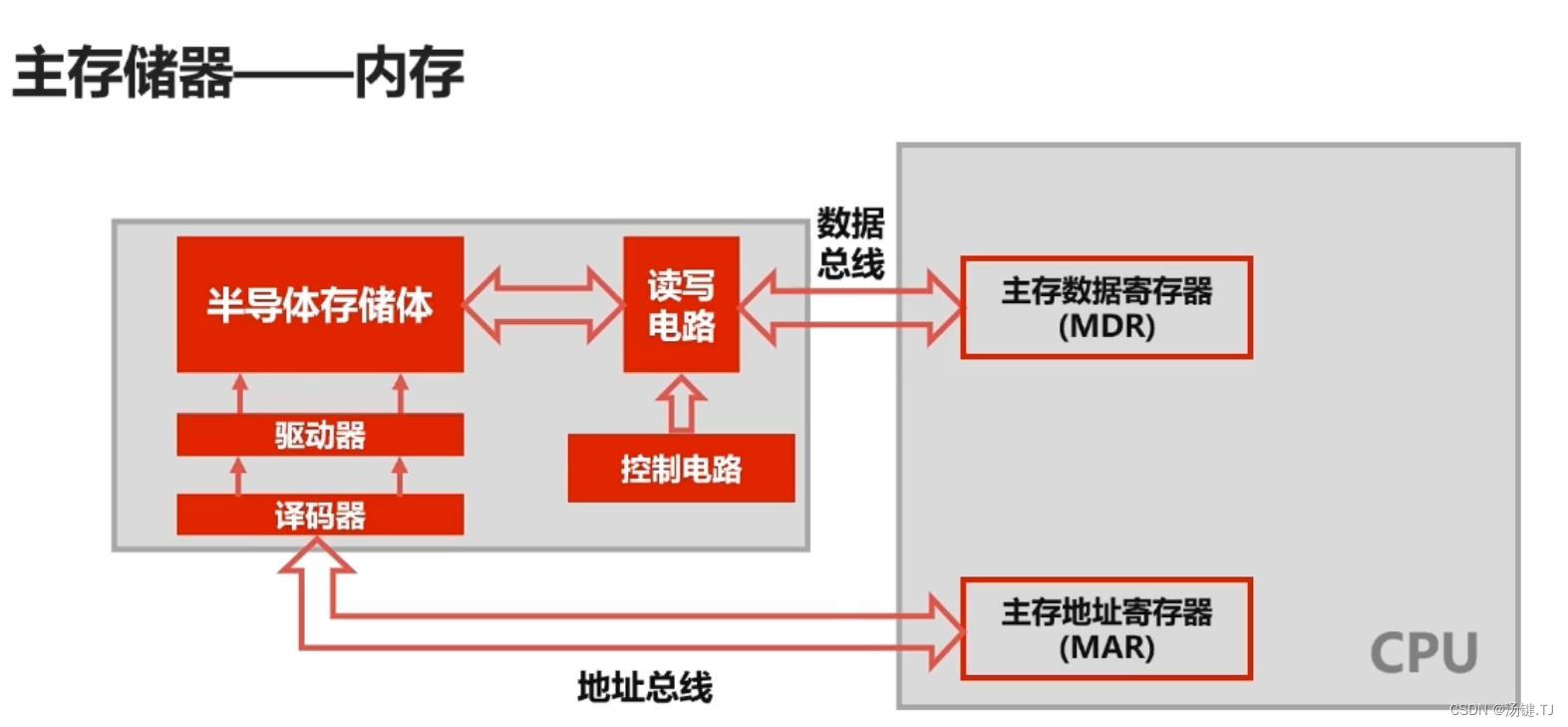

主存储器

- 是RAM(随机存取存储器)

- RAM通过电容存储数据,必须隔一段时间刷新一次

- 如果掉电,那么一段时间后将丢失所有数据

- 组成与CPU的交互

- 32位系统最多只能支持4GB内存

- 2的32次方=4×2的30次方=4GB

- 因为对于32位系统来说它的地址总线只有32位,所以它的寻址范围最多只有4GB的大小

-

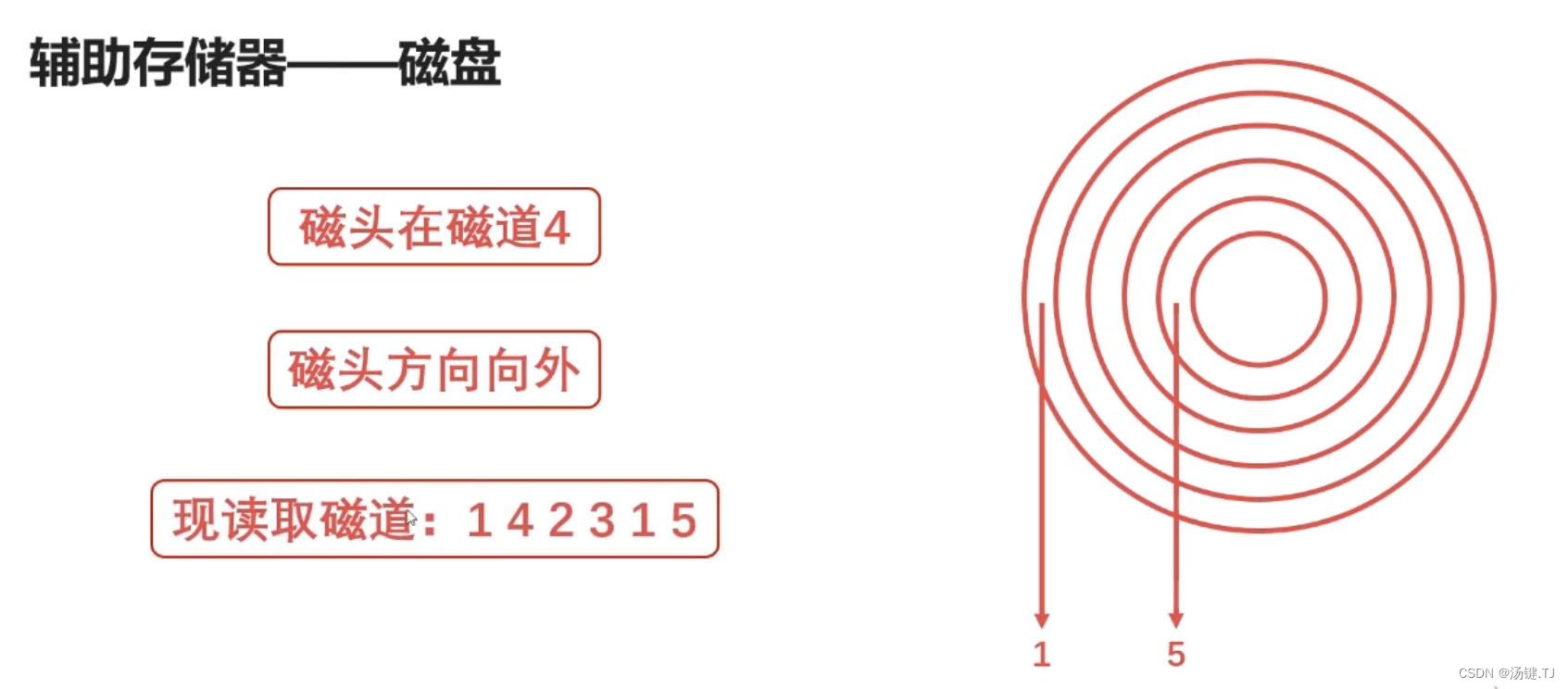

辅助存储器

- 表面是可磁化的硬磁特性材料

- 移动磁头径向运动读取磁道信息

- 调度算法

- 先来先服务算法

- 最短寻道时间优先算法

- 扫描算法(电梯算法)

- 循环扫描算法

- 以图示例子来介绍这4种算法

- 先来先服务算法

- 按顺序访问进程的磁道读写需求

- 1->4->2->3->1->5

- 最短寻道时间优先算法

- 与磁头当前位置有关

- 优先访问离磁头最近的磁道

- 4->5->3->2->1->1

- 扫描算法(电梯算法)

- 每次只往一个方向移动

- 到达一个方向需要服务的尽头再反方向移动

- 4->3->2->1->1->5

- 循环扫描算法

- 4->5->1->1->2->3