目录

概述

Hi3559A的视频输入模块可以对接前端MIPI_RX(Hi3559A的MIPI_RX不仅仅用作MIPI接口,还包括了LVDS、HiSPI等接口,因此称为combo设备)、BT.656、BT.1120、DC等视频接口,海思提供的sample中仅仅对接了sensor的MIPI_RX接口,而没有BT.656、BT.1120接口相关的例程。

本文详细描述了基于Hi3559AV100对接前端BT.1120接口的相关配置和操作说明,其他海思平台BT.656、BT.1120接口的开发流程和注意事项基本差不多。

本案例中,前端为FPGA通过标准BT.1120将视频输出到Hi3559A的VI CMOS2,输入的视频数据格式为1080P的YUV422,位宽为16bit,硬件上接VI CMOS2的16根数据线。

VI CMOS时钟配置

通过《Hi3559AV100_PINOUT_CN》可以看到,VI CMOS2和MIPI RX Port2/MIPI RX Port3共用引脚,且这两个接口功能并不是通过配置引脚复用寄存器来选择,而是通过使能对应接口时钟来选择。

根据《Hi3559A╱C V100 ultra-HD Mobile Camera SoC 用户指南》中MIPI_RX频率配置寄存器(PERI_CRG65),要使能VI CMOS2时钟,应当把PERI_CRG65的bit[11:9]置为111b:

海思提供的sys_config.ko驱动中就有关于VI CMOS0/1/2接口时钟的配置代码,可以直接用起来:

static void coms_clock_config(int index)

{

if(0 == index)

{

reg_write32(0x5 << 15, 0x7 << 15, (unsigned long)reg_crg_base+0x0104);

}

else if(1 == index)

{

reg_write32(0x6 << 21, 0x7 << 21, (unsigned long)reg_crg_base+0x0104);

}

else if(2 == index)

{

reg_write32(0x7 << 9, 0x7 << 9, (unsigned long)reg_crg_base+0x0104);

}

}注意:上述代码是修改后的,海思原本提供的sys_config.c中的这段代码是有问题的。

为了在驱动中调用这段代码从而使能VI CMOS2的时钟,在加载load3559av100_multicore脚本时应带参数-sensor2 bt1120:

./load3559av100_multicore -i -sensor2 bt1120同理,如果使用VI CMOS0或VI CMOS1,则修改为-sensor0或-sensor1即可。这样就可以将参数传递给sys_config.ko并执行coms_clock_config进行时钟配置。详情请自行阅读load3559av100_multicore脚本及sys_config.c源码。

BT.1120接口配置

BT.1120接口属性还是通过MIPI_RX的HI_MIPI_SET_DEV_ATTR进行配置。

需要注意的是,结构体combo_dev_attr_t的devno不是VI DEV号,也不是MIPI RX设备号(这里也根本没使用MIPI接口),而是VI CMOS号,本案例使用的是Hi3559A的VI CMOS2,因此devno = 2。input_mode固定为INPUT_MODE_BT1120。data_rate固定为MIPI_DATA_RATE_X1(仅MIPI的设备0和SLVS的设备0支持MIPI_DATA_RATE_X2,《MIPI使用指南》中有说明)。

其他参数没什么特别要注意的,请参考《MIPI使用指南》。

本案例中combo_dev_attr_t完整配置如下:

combo_dev_attr.devno = 2;

combo_dev_attr.input_mode = INPUT_MODE_BT1120;

combo_dev_attr.data_rate = MIPI_DATA_RATE_X1;

combo_dev_attr.img_rect.width = 1920;

combo_dev_attr.img_rect.height = 1080;VI DEV配置

VI DEV负责对BT.1120时序进行解析,并传递给后端模块。

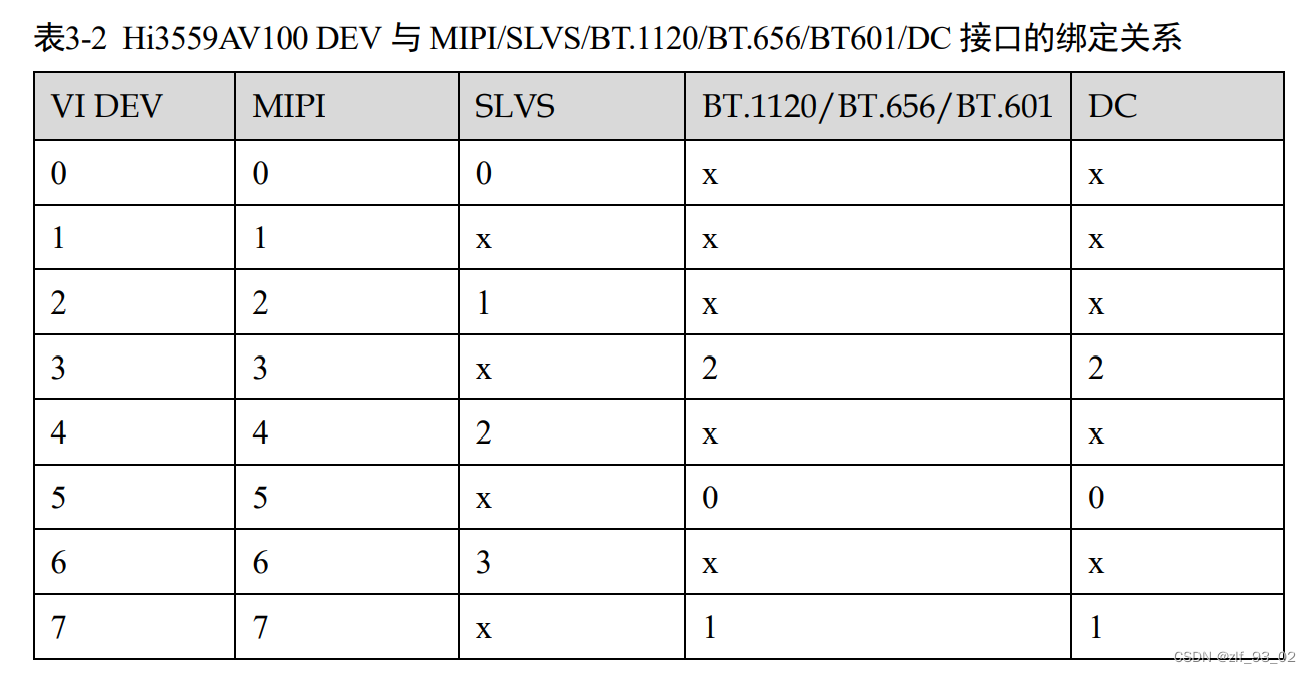

Hi3559A固定配置了VI CMOS和VI DEV之间的绑定关系,不支持修改。

本案例使用的是Hi3559A的VI CMOS2,从上表可知对应的DEV为3,因此必须使用VI DEV3。同理,如果使用的是VI CMOS0,则DEV为5,使用的是VI CMOS1,则DEV为7。

需要注意的是,结构体VI_DEV_ATTR_S的enIntfMode为VI_MODE_BT1120_STANDARD,enScanMode为VI_SCAN_PROGRESSIVE,因为Hi3559A的BT.1120是不支持隔行扫描的。

本案例中VI_DEV_ATTR_S完整配置如下:

stDevAttr.enIntfMode = VI_MODE_BT1120_STANDARD;

stDevAttr.enWorkMode = VI_WORK_MODE_1Multiplex;

stDevAttr.au32ComponentMask[0] = 0xff000000;

stDevAttr.au32ComponentMask[1] = 0x00ff0000;

stDevAttr.enScanMode = VI_SCAN_PROGRESSIVE;

stDevAttr.as32AdChnId[0] = -1;

stDevAttr.as32AdChnId[1] = -1;

stDevAttr.as32AdChnId[2] = -1;

stDevAttr.as32AdChnId[3] = -1;

stDevAttr.enDataSeq = VI_DATA_SEQ_VUVU;

stDevAttr.enInputDataType = VI_DATA_TYPE_YUV;

stDevAttr.stSize.u32Width = 1920;

stDevAttr.stSize.u32Height = 1080;

stDevAttr.stBasAttr.stSacleAttr.stBasSize.u32Width = stDevAttr.stSize.u32Width;

stDevAttr.stBasAttr.stSacleAttr.stBasSize.u32Height = stDevAttr.stSize.u32Height;

stDevAttr.stWDRAttr.enWDRMode = WDR_MODE_NONE;

stDevAttr.enDataRate = DATA_RATE_X1;VI PIPE配置

到这一步为止,VI DEV已经可以正确解析BT.1120时序并传递给后端模块了,前端对接BT.1120就完成了。VI PIPE的配置与前端时序无关,参考sample和MPP开发手册就可以了。

需要注意的是,这里必须把VI ISP模块关闭,即结构体VI_PIPE_ATTR_S的成员bIspBypass置为HI_TRUE。一般前端对接sensor时才需要开VI ISP,而对接数字视频信号时不需要。

本案例中VI_PIPE_ATTR_S完整配置如下:

stPipeAttr.enPipeBypassMode = VI_PIPE_BYPASS_NONE;

stPipeAttr.bYuvSkip = HI_FALSE;

stPipeAttr.bIspBypass = HI_TRUE;

stPipeAttr.u32MaxW = 1920;

stPipeAttr.u32MaxH = 1080;

stPipeAttr.enPixFmt = PIXEL_FORMAT_YVU_SEMIPLANAR_420;

stPipeAttr.enCompressMode = COMPRESS_MODE_NONE;

stPipeAttr.enBitWidth = DATA_BITWIDTH_8;

stPipeAttr.bNrEn = HI_FALSE;

stPipeAttr.bSharpenEn = HI_FALSE;

stPipeAttr.stFrameRate.s32SrcFrameRate = -1;

stPipeAttr.stFrameRate.s32DstFrameRate = -1;

stPipeAttr.bDiscardProPic = HI_FALSE;VI CHN配置

同样,VI CHN的配置与前端时序无关,参考sample和MPP开发手册就可以了。

本案例中VI_CHN_ATTR_S完整配置如下:

stChnAttr.stSize.u32Width = 1920;

stChnAttr.stSize.u32Height = 1080;

stChnAttr.enPixelFormat = PIXEL_FORMAT_YVU_SEMIPLANAR_420;

stChnAttr.enDynamicRange = DYNAMIC_RANGE_SDR8;

stChnAttr.enVideoFormat = VIDEO_FORMAT_LINEAR;

stChnAttr.enCompressMode = COMPRESS_MODE_NONE;

stChnAttr.stFrameRate.s32SrcFrameRate = -1;

stChnAttr.stFrameRate.s32DstFrameRate = -1;问题

调试过程中,查看/proc/umap/vi发现,IntCnt和LostFrame同时在增加,且总是相差2,后来通过FPGA示波器发现送出来的时钟不对,硬件修改了参考时钟后解决。