这第三节实验课的内容其实不是很多,主要是对于第二节课的组合逻辑的内容用代码写一遍,而不是调用现成的IPcore。写好之后再仿真一下。

新建工程创建源文件,这些基本的流程就不累述了,忘记的同学可以去我的第一篇课程博客里面去走一遍:【课程记录】win10 第一次安装使用vivado 2017.2 并建立project

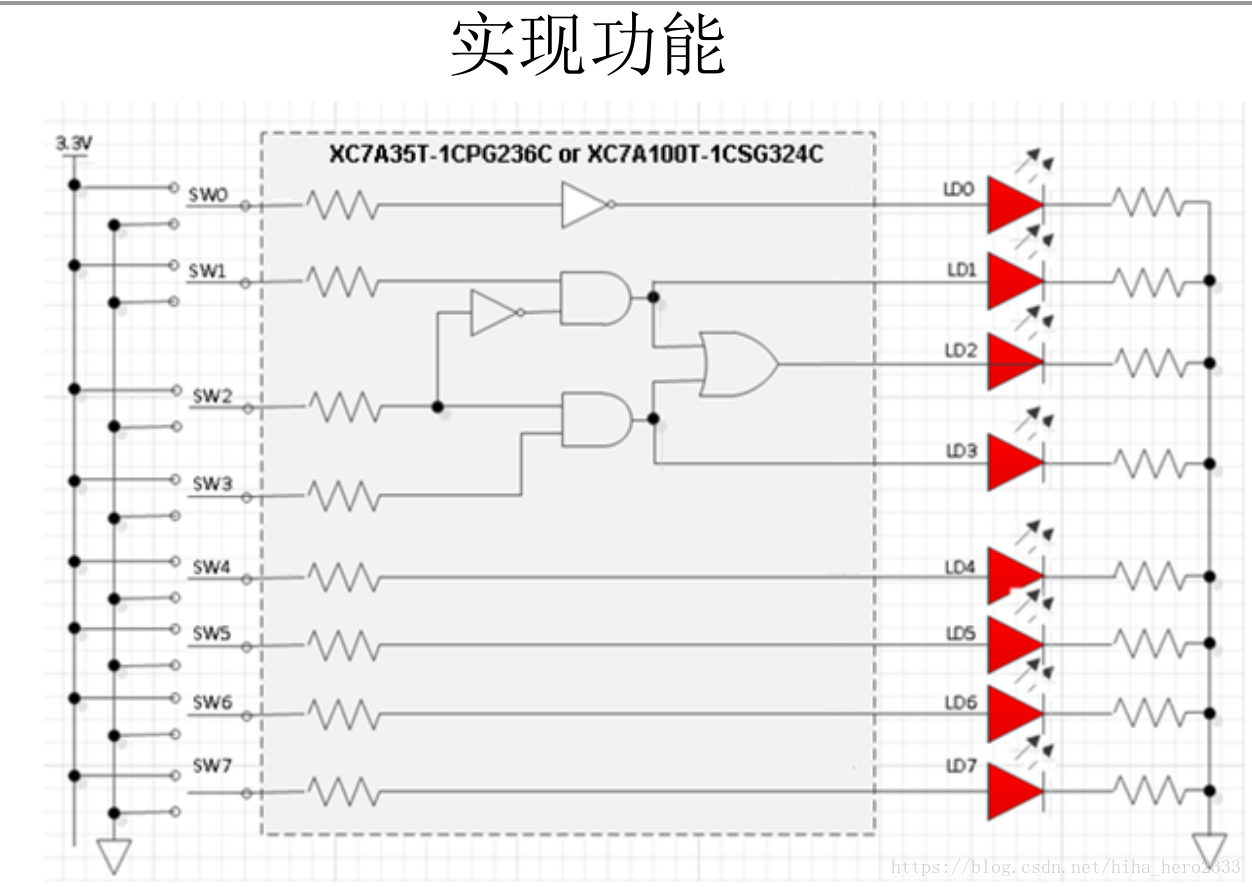

再看回我们要实现的逻辑电路图:

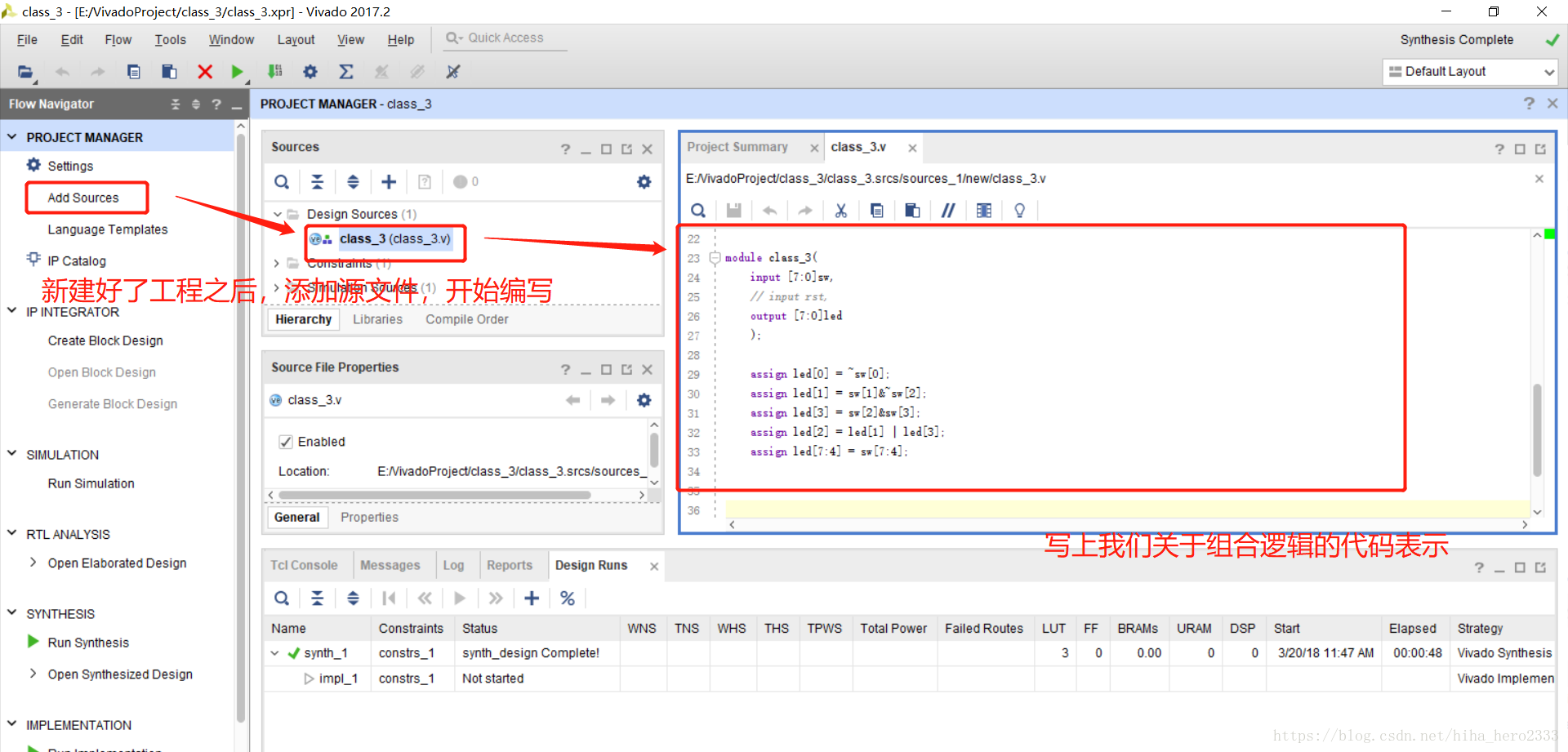

verilog 代码如下:

module class_3(

input [7:0]sw,

// input rst,

output [7:0]led

);

assign led[0] = ~sw[0];

assign led[1] = sw[1]&~sw[2];

assign led[3] = sw[2]&sw[3];

assign led[2] = led[1] | led[3];

assign led[7:4] = sw[7:4];

endmodule 如果对比我们使用IPcore自动生成的代码会发现,自己编写的代码会简洁明了很多,而且注意到我们在定义输入输出端口的时候,直接用“位数”实现led类似数组的定义,输入端8位sw的具体某一位可以用 sw[num] 来访问,定义。(输出端led同理)

这样做还有一个好处是,这样的定义和我们本来有的约束文件“Basys3_Master.xdc” 里面规定的端口名一致,就不用重复改动了。

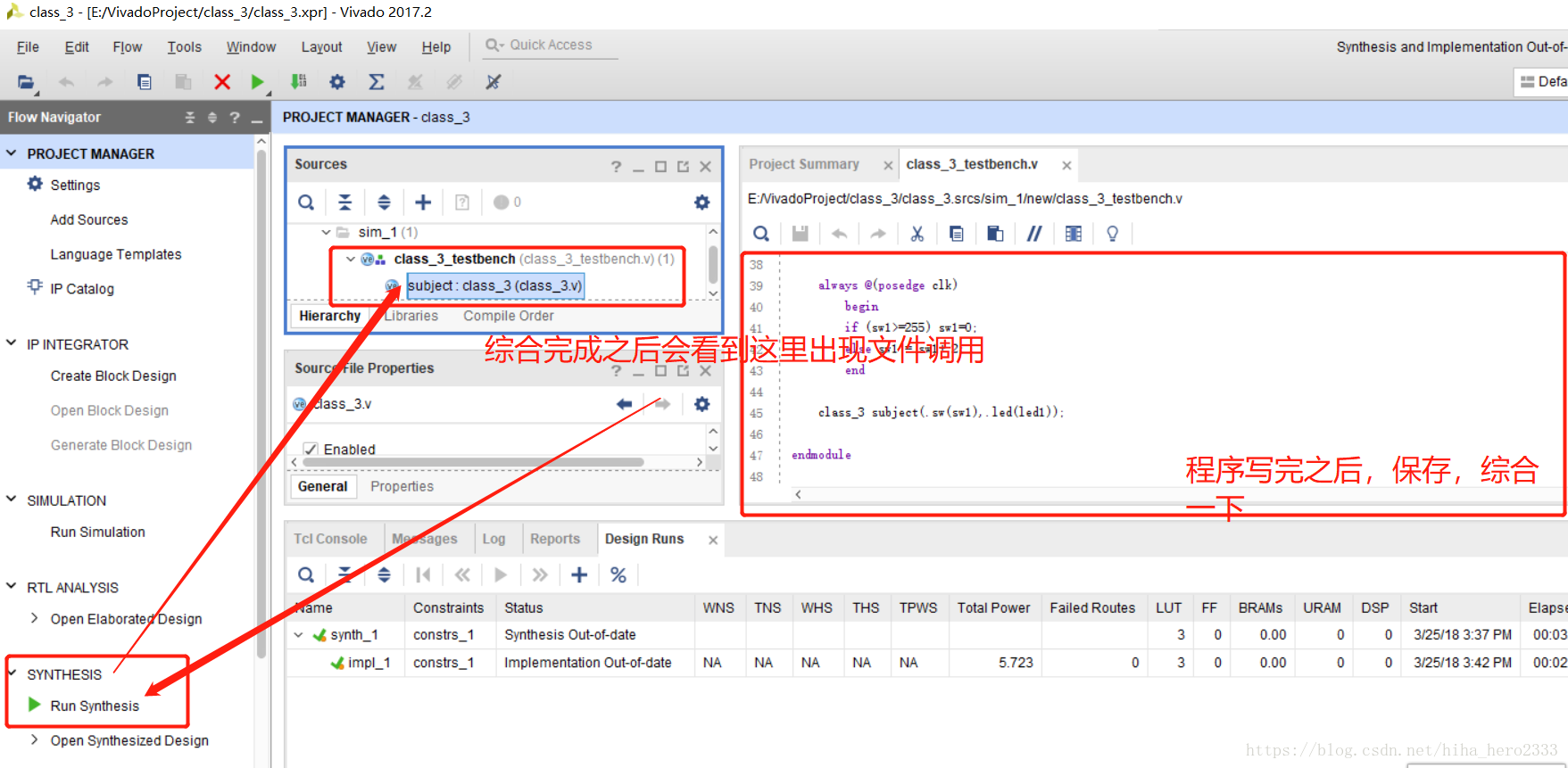

写好代码之后,编译综合(run synthesis) 》添加约束文件“Basys3_Master.xdc” 》运行应用(run implementation)》 generate bitstream 等等操作也相信大家都会了啦((;´༎ຶД༎ຶ`) 真相是我不想重复写了)

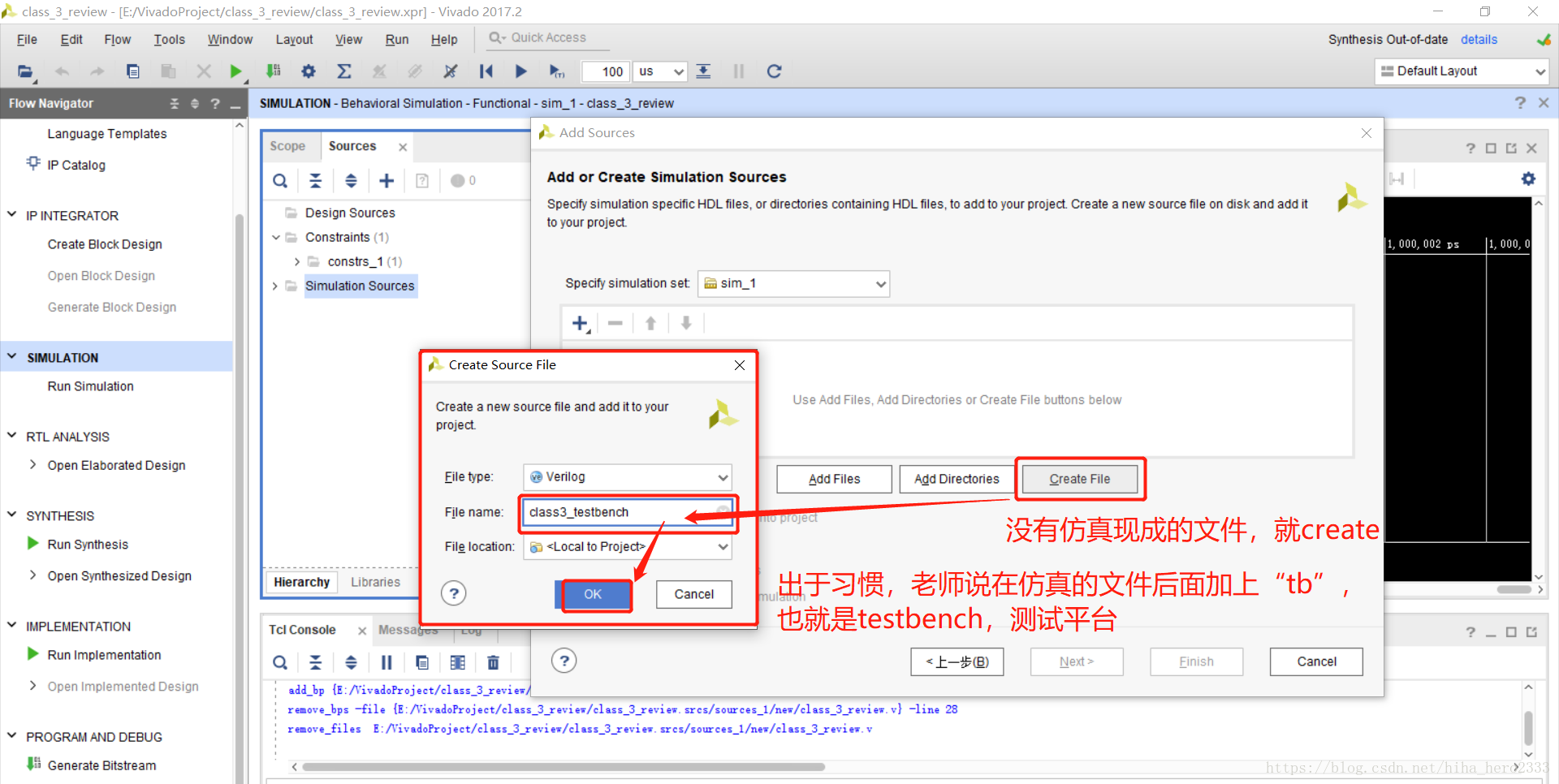

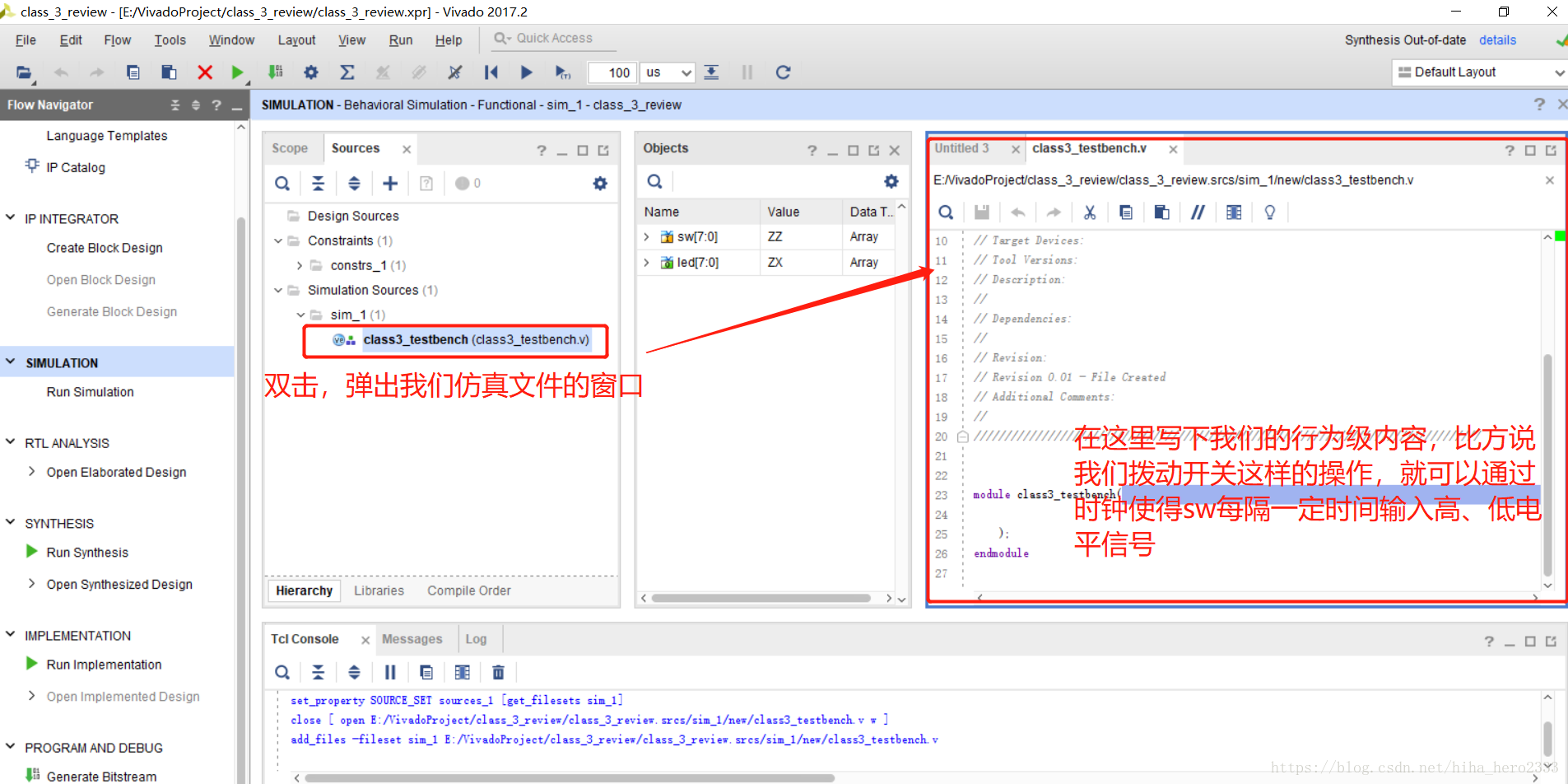

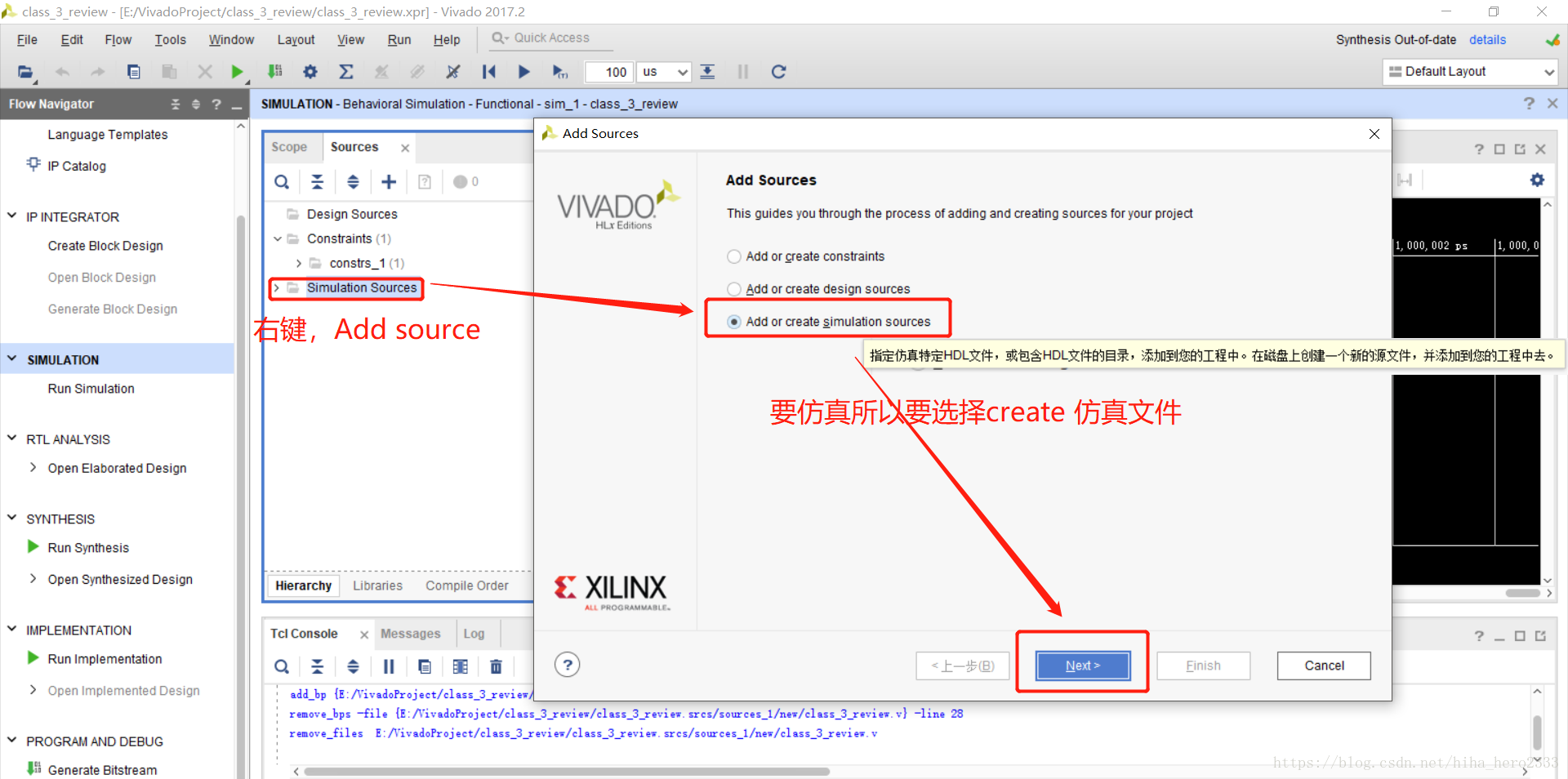

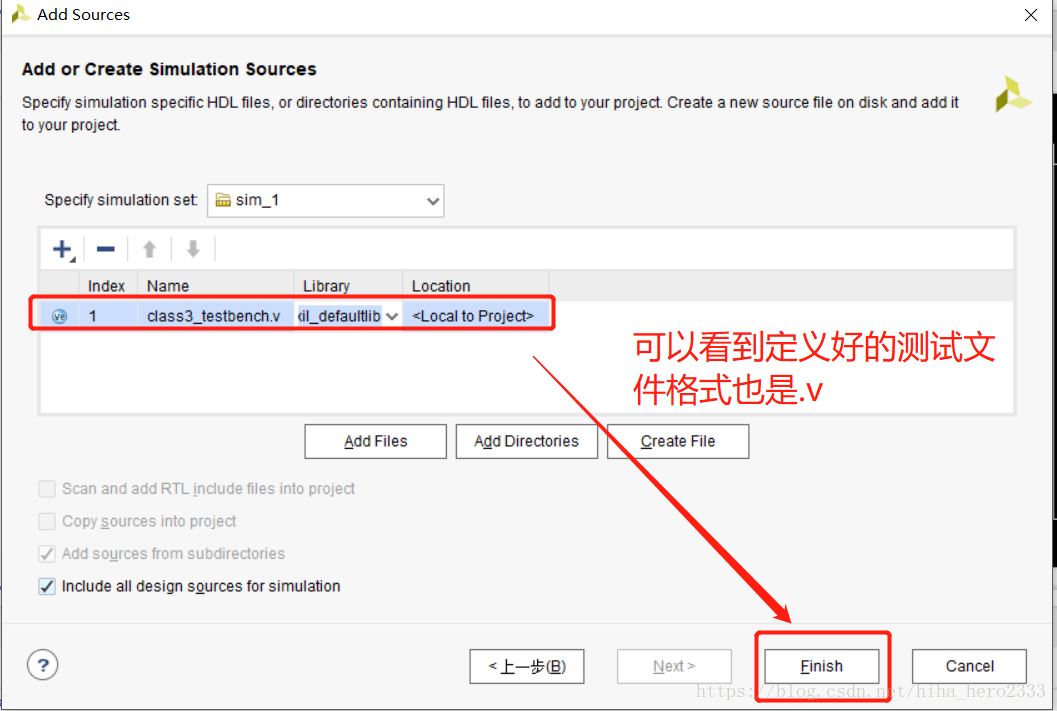

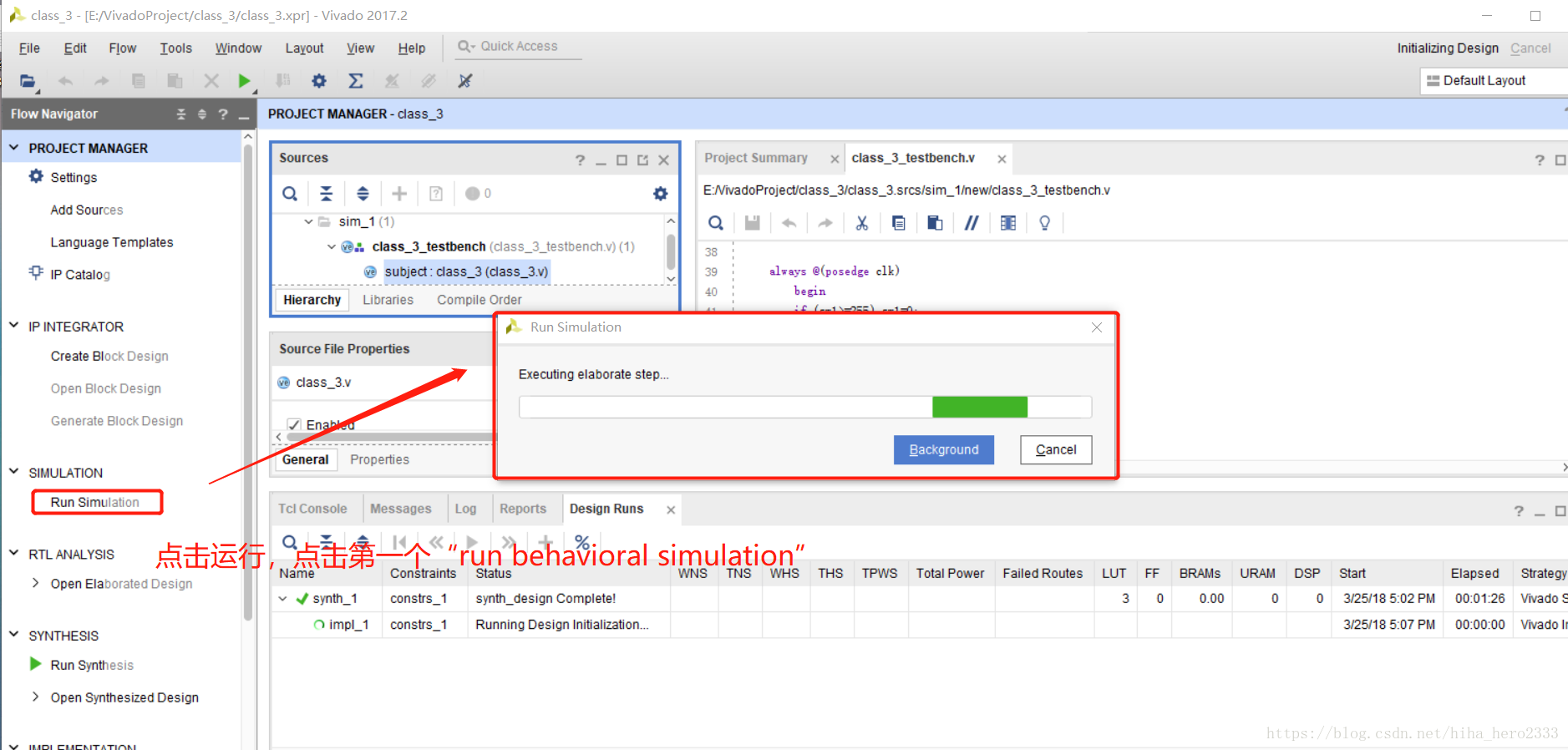

我们这一节课的主要内容是学会仿真,其实只要综合完成之后,就可以直接进入仿真环节 run simulation 了。

module class3_testbench();//仿真就不需要什么端口

reg clk;

reg[7:0]sw;

wire[7:0]led;

initial //定义信号的初始状态

begin

clk = 0;

sw = 0;

end

always //产生虚拟时钟信号

begin

#5 clk=~clk; //#5 表示延时5个单位时间,单位时间在.v文件顶部可以查看,为1ns,说明延时5ns

end

always @(posedge clk) //这一部分模拟开关切换,选clk的信号上升沿触发

begin

if(sw>=255) sw = 0;

else sw = sw+2; // 这样一来,由于clk的信号上升沿10s才有一次,所以sw在10ns下才+2一次

end

//最后这个最关键↓

class_3 u1(.sw(sw),.led(led)); //说明了仿真文件与源文件的调用,其中class_3 是源文件HDL的名字,u1是class_3.v实例化的一个对象的名字(可以联系c语言struct的用法理解),.sw()是说明源文件与仿真文件的对应关系,括号()里面的端口名是仿真文件中的端口名称。

endmodule

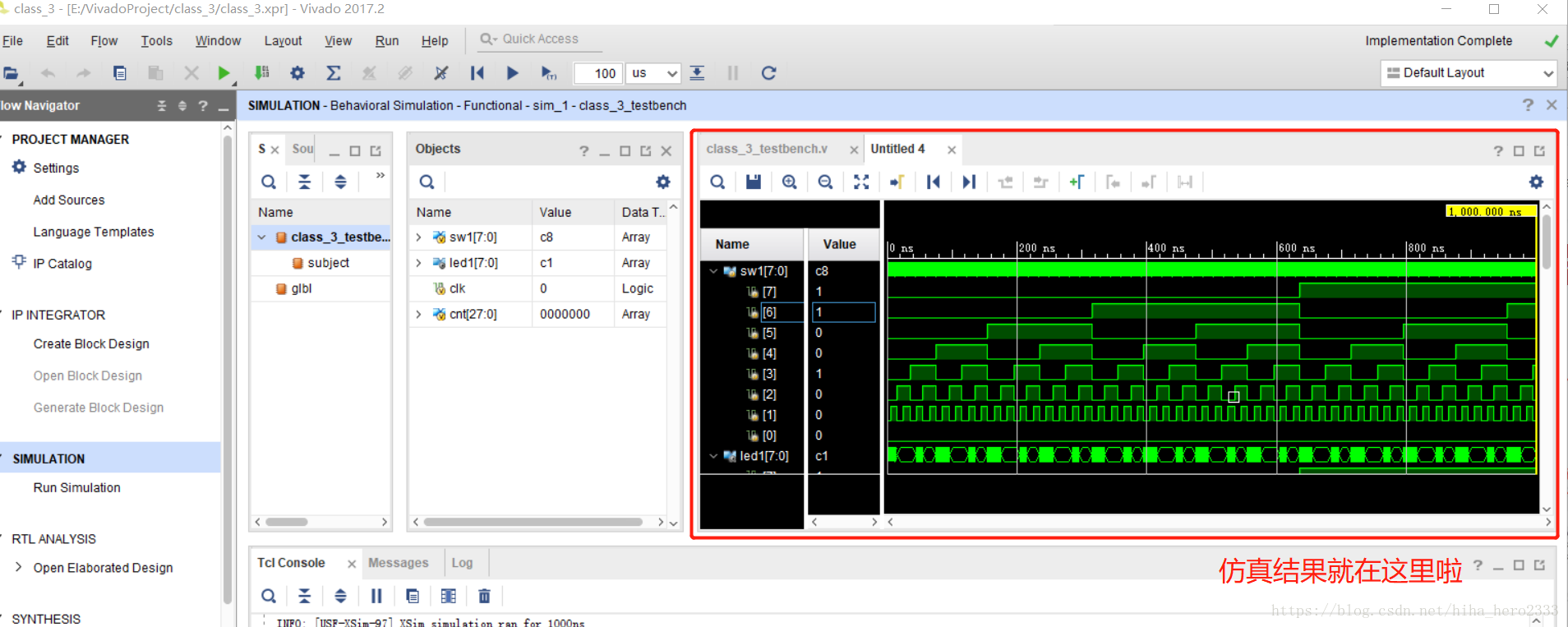

移动右侧的黄色标签,左边对应的信号值就会改变。可以对照sw 与led的对应关系是否满足最初的要求。

1、仿真就是产生被测对象所需的输入信号,观察对应的输出信号是否满足工程设计要求;

2、针对仿真还有很多细节的东西,希望在源程序的编写、断点设置与单步调试技巧、时序仿真及时间约束等方面多多加强。