组合逻辑电路

前言:

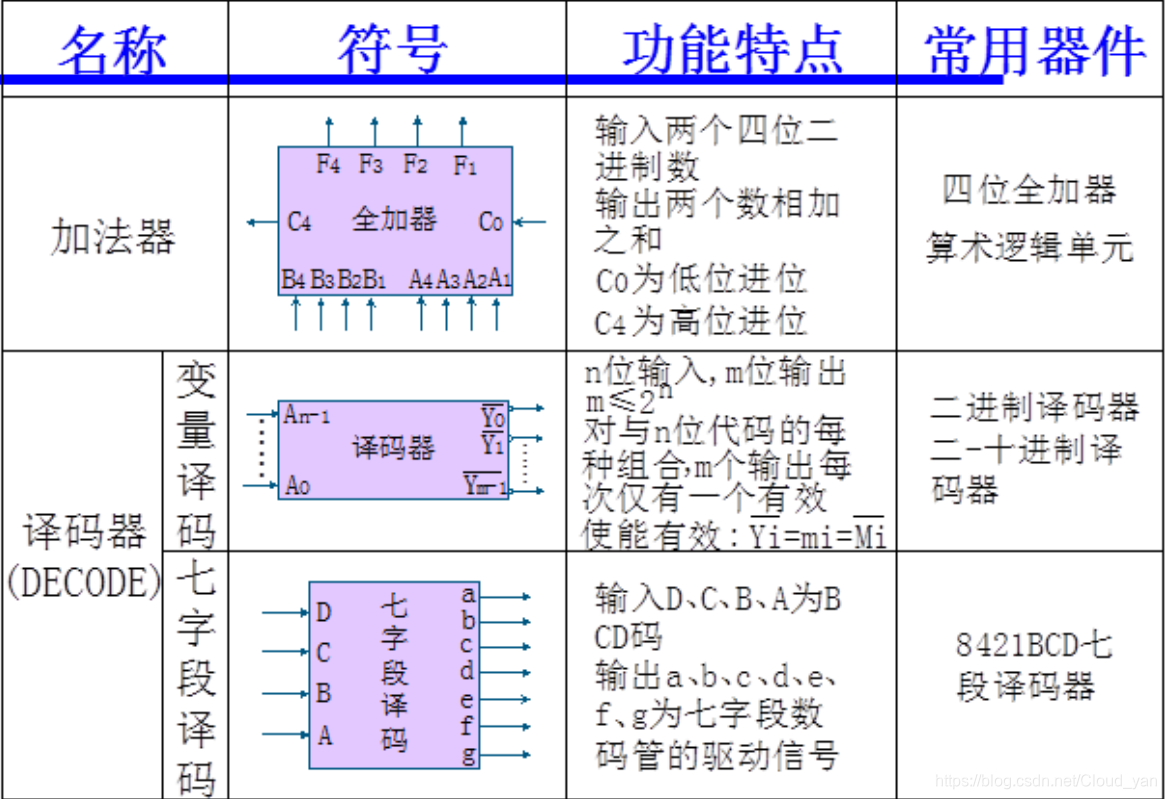

本章当中,数据选择器和译码器是比较重要的。因为这两个电路可以出题,来考察。相较于前两者,编码器,数据分配器,数值比较器,加法器,减法器,应该是记忆即可。

译码器与数据选择器的例题可以前去好好做一下。

下面尽是些课本概念,你看与不看都可。因为毕竟是笔者为记忆而写的,也有一个较为清晰的分块,你可选择且看一下的。

逻辑电路可分为两类:

- 组合逻辑电路(组合电路):任一时刻的稳态只取决于该时刻的输入,与原状态无关

- 时序逻辑电路(时序电路):除与现时的输入外,还与电路的原状态有关

半加器:

只考虑了本位的两个数二进制数相加,而没有考虑低位的进位

全加器:

不只是本位的两个二进制数的相加,来自低位的进位也一起相加

全加器真值表:

| Ai(被加数) | Bi(加数) | Ci (低位向本位的进位) | Ci+1(进位) | Si(本位和) |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

组合逻辑电路的设计

- 逻辑抽象:确定实际问题的逻辑含义

- 列真值表

- 用逻辑代数或卡诺图进行化简

- 写出逻辑表达式

- 画出逻辑电路图

中规模(MSI)组合逻辑电路

译码器

编码器

数据选择器

数据分配器

数码比较器

加法器

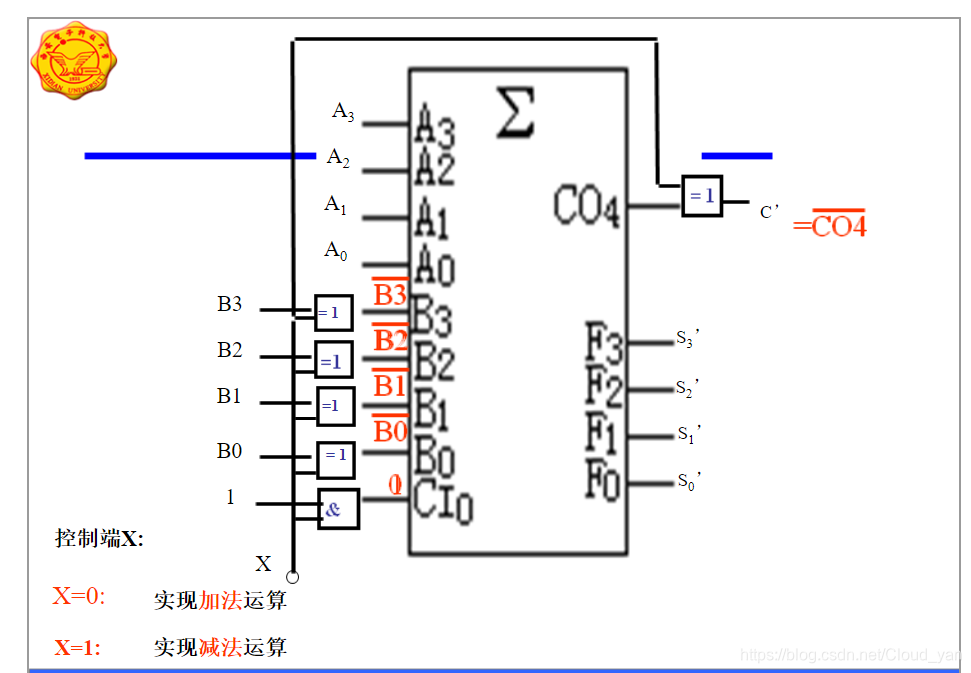

减法器

编码器

编码:将特定含义的信息用二进制代码表示的过程

编码器:实现编码功能的电路,m个输入信号、n位二进制代码输出。

m<=2n,当m=2n时,称为二进制编码器。

m=10,n=4时,称为二–十进制编码器

编码器分为:

普通编码器:任何时刻只允许输入一个有效信号,不允许出现多个输入同时有效的情况,否则编码器将产生错误的输出。

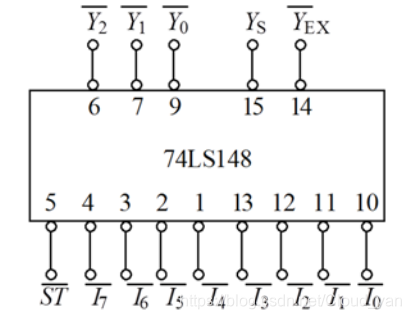

优先编码器:在一定条件下允许多个输入同时有效,能根据事先安排好的优先顺序只对优先级高的有效输入信号进行编码。

常见优先编码器:

二进制优先编码器:输入端和输出端均为低电平有效

其真值表为:

二–十进制优先编码器(BCD优先编码器)

输入,输出端均为低电平有效

给每个输出端加一个反相器,即可将反码输出的BCD码转换成正常的BCD码

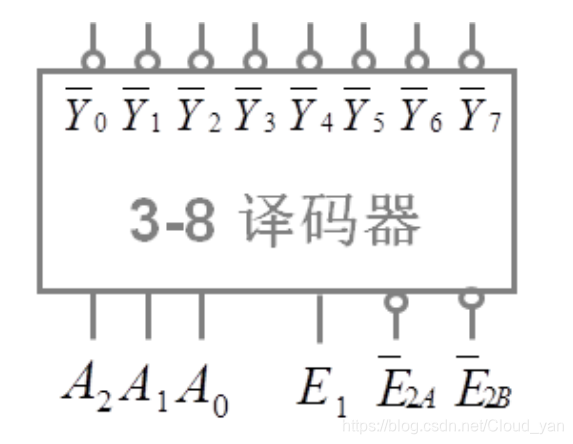

译码器

译码:编码的逆过程

译码器有两种:

变量译码器(唯一地址译码器):常用于计算机中将一个地址代码转换成一个有效信号

显示译码器:用于驱动数码管显示数字或字符

n个输入端,m个输出端,m<=2n

-

二进制译码器

n位输入,2n位输出

输出端,低电平有效

E为使能端,低电平有效

当E=0时,允许译码器工作。当E=1时,译码器禁止工作,此时,所有Y均为高电平。

如果用Yi表示 i 端的输出,mi表示输入地址变量A1、A0的一个最小项,则E=0时,输出函数可以表示成:

下面是2–4译码器的表示符号:

对于3–8译码器:

只有当E1为高,E2,E3都为低时,该译码器才能有有效信号的输出。如有一个不满足,则译码器不工作,输出全为高。

下面是3–8译码器的表示符号:

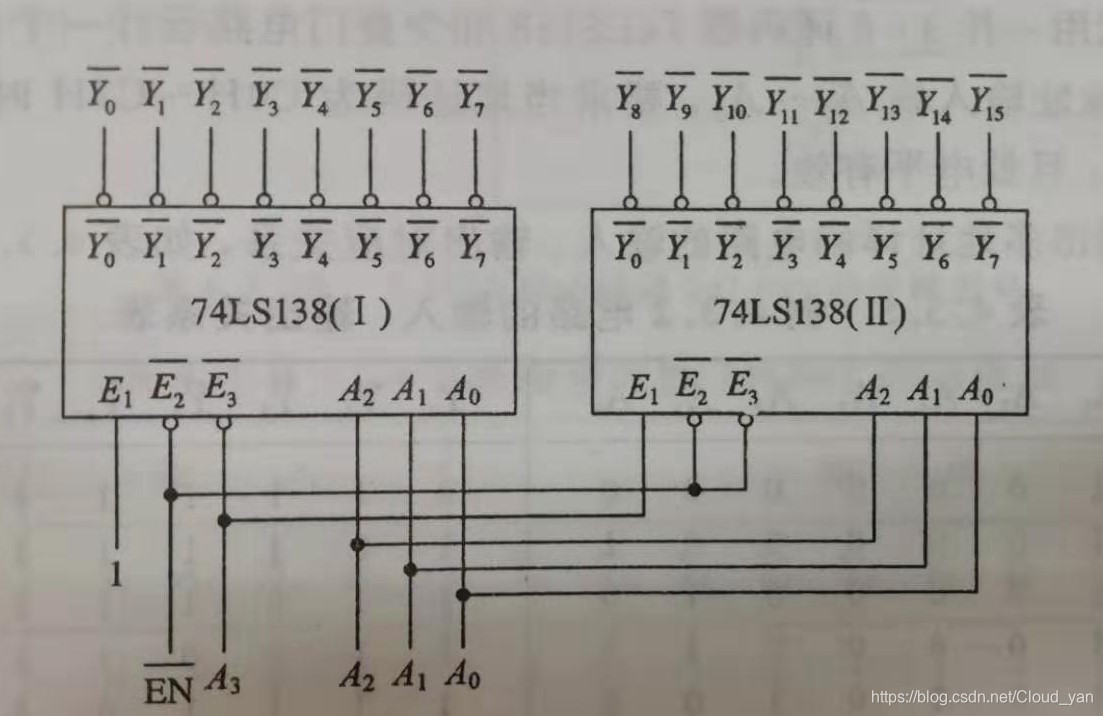

译码器的扩展

通过采用两片3–8译码器可以构成一个4–16译码器:

由A3来对两片3–8译码器进行选择。

A1、A2、A0变化时,通过A3的选择,来进行不同的输出。

译码器的应用:

(1) 实现逻辑函数

(2) 实现存储系统的地址译码

(3) 带使能端的译码器可用作数据分配器或脉冲分配器请看书上例题:P72页

例题:用译码器实现函数。

用特定的地址来选定译码器 -

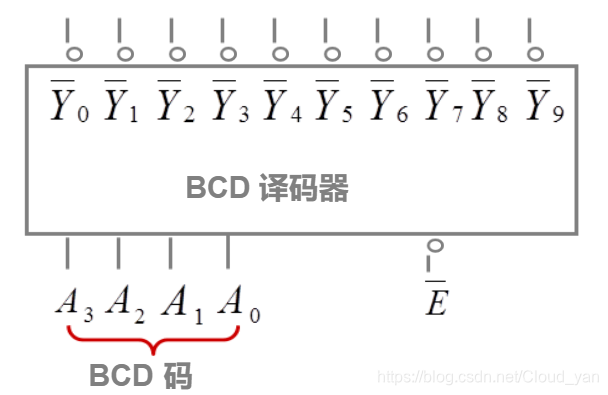

二–十进制译码器

BCD译码器,功能是将输入的一位BCD码,译成10个高、低电平输出信号。

当输入一个BCD码时,就会在它所表示的十进制数的对应输出端产生一个低电平有效信号。

如果输入的是伪码(非法码),则均无低电平信号产生,即译码器拒绝翻译。

下面是它的逻辑符号:

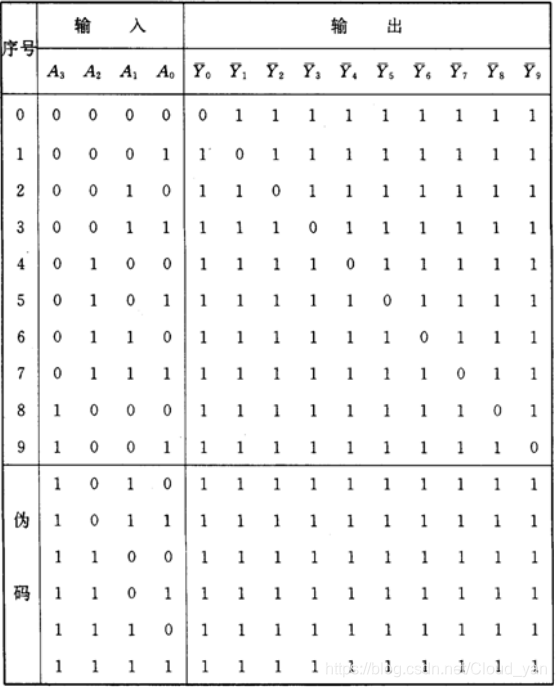

它的真值表:

-

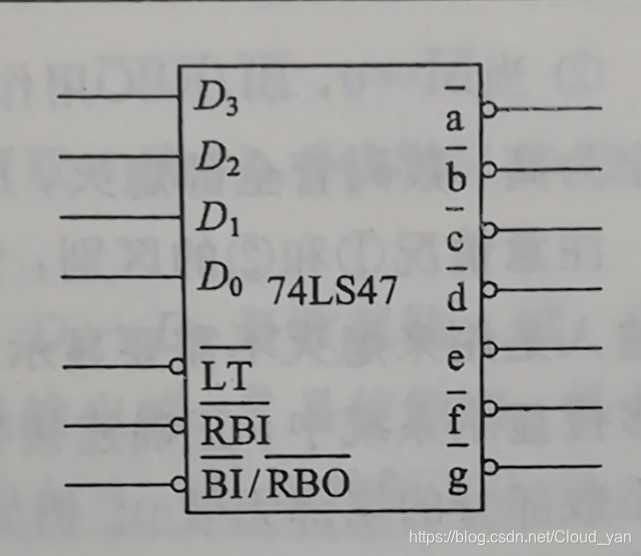

显示译码器

数码显示器(数码管):用于显示数字、文字或符号的器件

显示译码器:用来驱动数码管显示数字或字符的组合逻辑部件。

下面是74LS47的逻辑符号:

D为输入

a/b/c/d/e/f/g:输出端,低电平输出

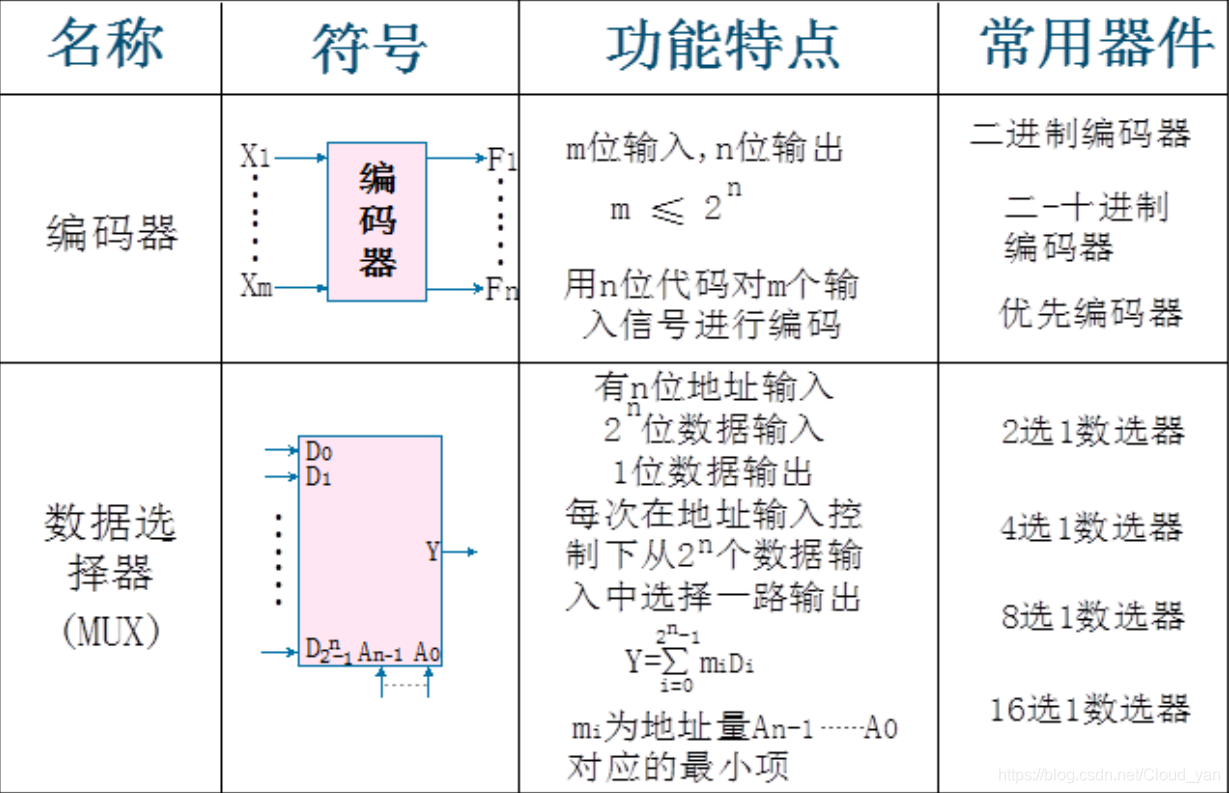

数据选择器(多路选择器,MUX)

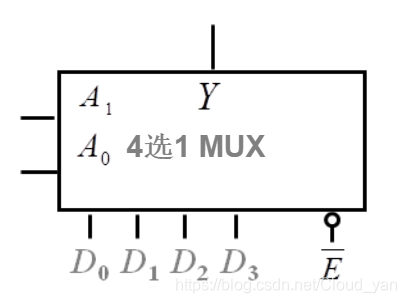

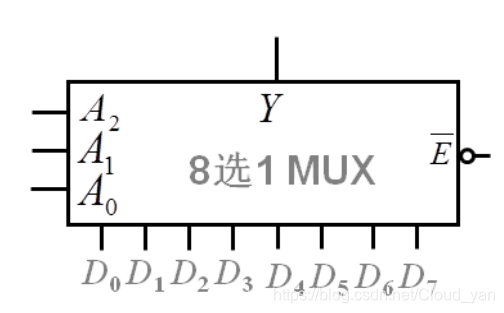

n位地址输入,2n位数据输入,1位输出

在地址输入的控制下,从多路输入数据中选择一路输出。

D为数据输入端

A为地址输入端

E为使能端,低电平有效

下面是4选1MUX的逻辑符号:

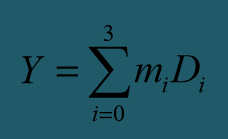

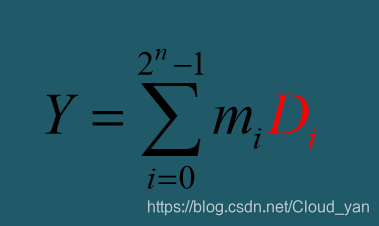

其函数表达式为:

下面是8选1MUX的逻辑符号:

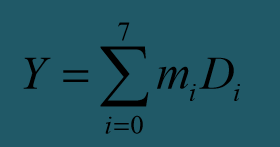

其函数表达式为:

对于有n个地址输入端的数据选择器来说:

数据选择器的扩展:

利用使能端进行扩展。

数据选择器的应用(有题):

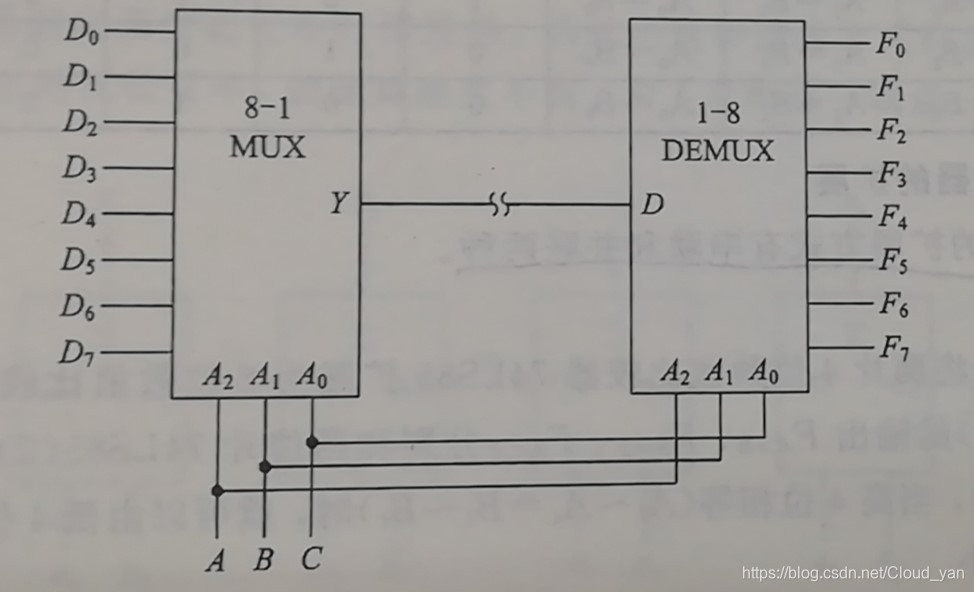

实现多路信号的分时传送

实现组合逻辑函数

实现并行数据到串行数据的转换

产生序列信号

例题:P81页

实现组合逻辑电路

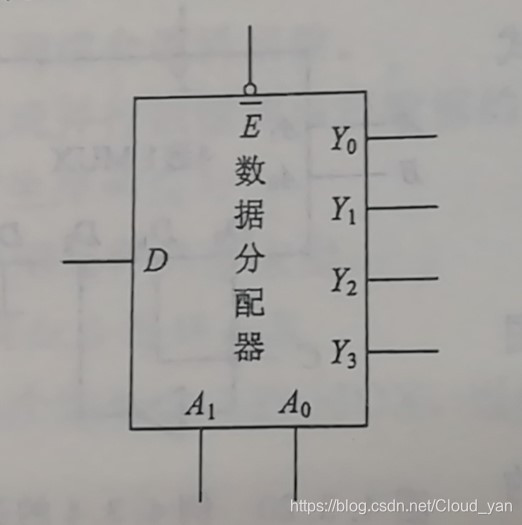

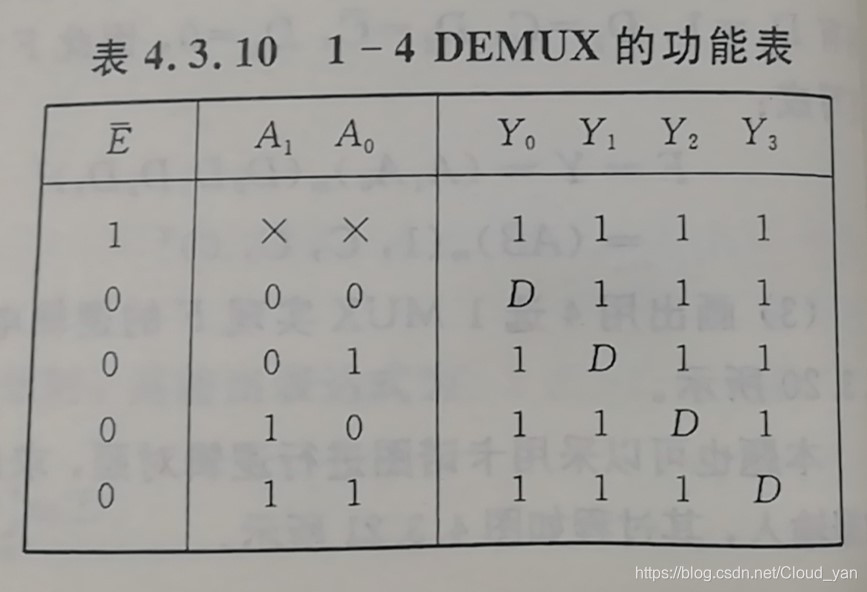

数据分配器

多路分配器:功能与数据选择器相反,可以将一路输入数据按n位地址分送到22个数据输出端上

其逻辑符号为:

其功能表为:

凡是具有使能端的译码器都可以用作数据分配器

数据分配器常与数据选择器联用,以实现多通道数据分时传送

数值比较器

数值比较器是对两个位数相同的二进制数进行数值比较,并判定其关系大小的组合逻辑电路。

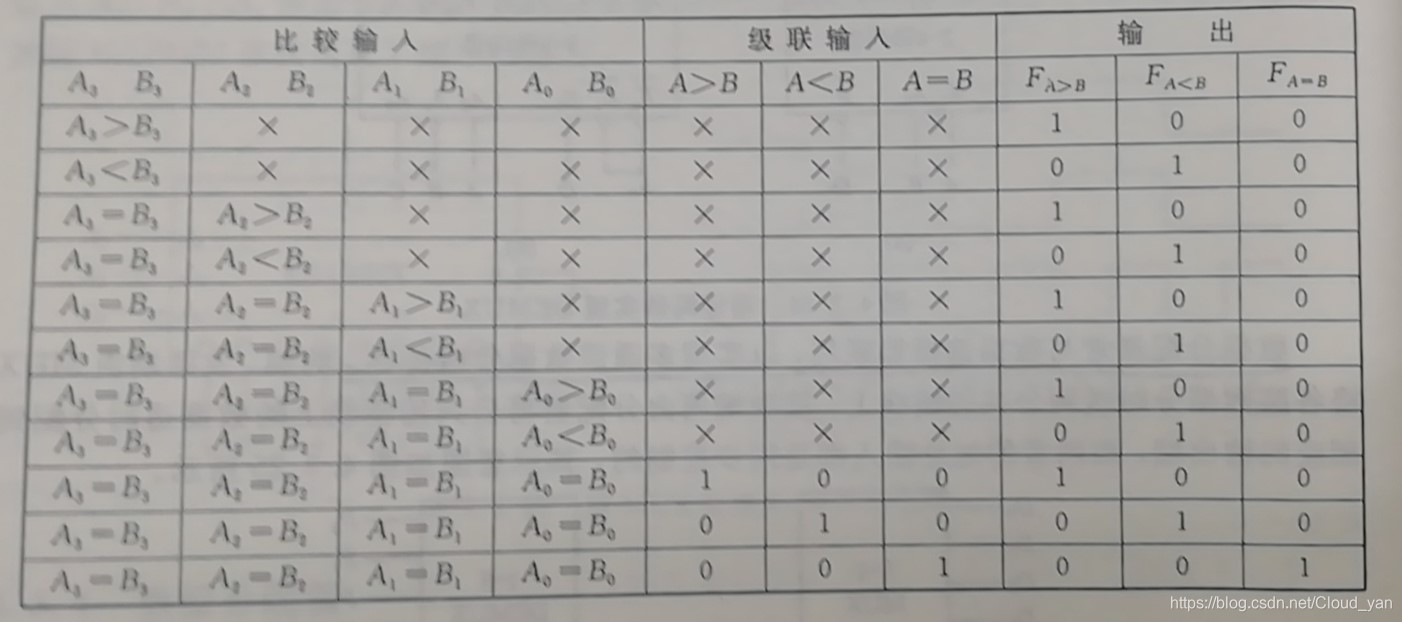

比较原则:

先从高位比起,高位大的数值一定大

如高位相等,则再比较低位数,最终结果由低位的比较结果决定。

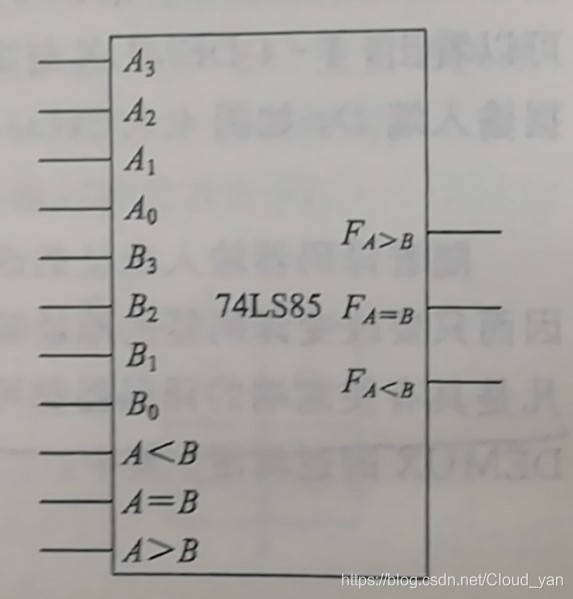

其逻辑符号为:

A3 ~ A0、B3 ~ B0是待比较的4位二进制数输入端。

A<B/A=B/A>B:是低位比较结果

其功能表为:

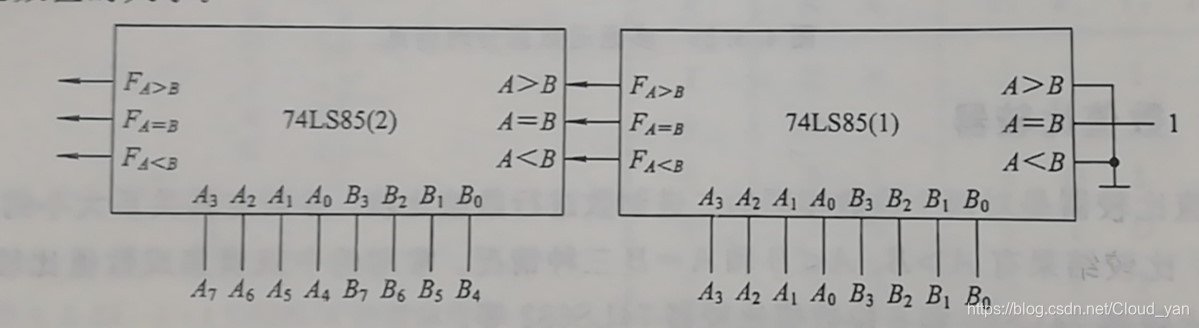

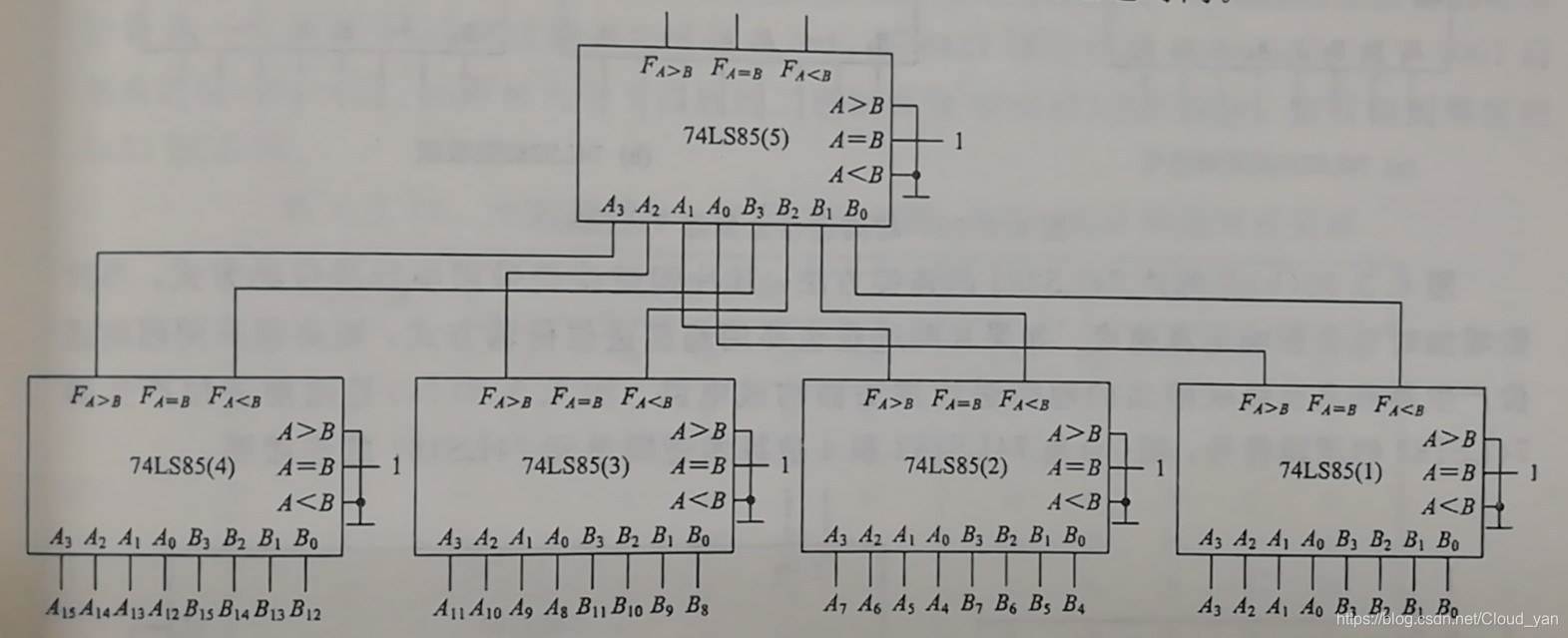

数值比较器的扩展方式有串联和并联两种。

串联:

并联:

当比较的位数比较多,且速度要求快时,可以采用并联方式扩展。

加法器

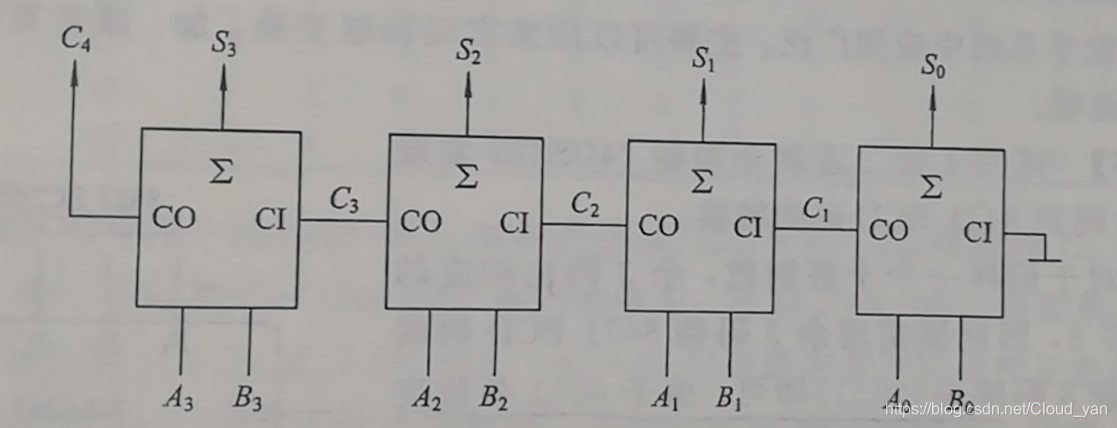

当要实现两个多位二进制数相加时,可采用并行相加。串行进位的方法实现。但这种方法运算速度不高。

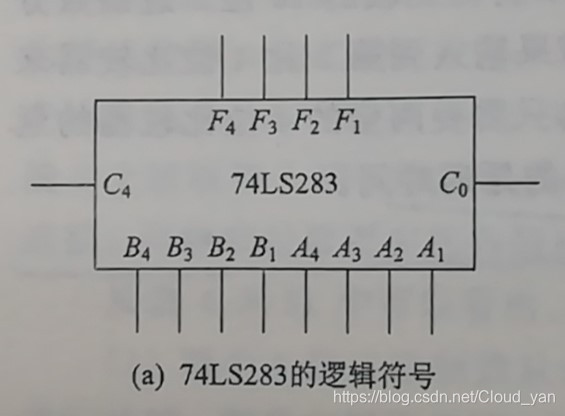

超前进位加法器(74LS283)

超前进位技术:各位进位信号仅由加数、被加数和最低位的进位信号C0决定,而与其他进位无关。

其逻辑符号为:

其中:

A4到A1,B4到B1分别为4位加数和被加数输入端。

F4到F1为4位和输出端

C0为进位输入端

C4为进位输出端

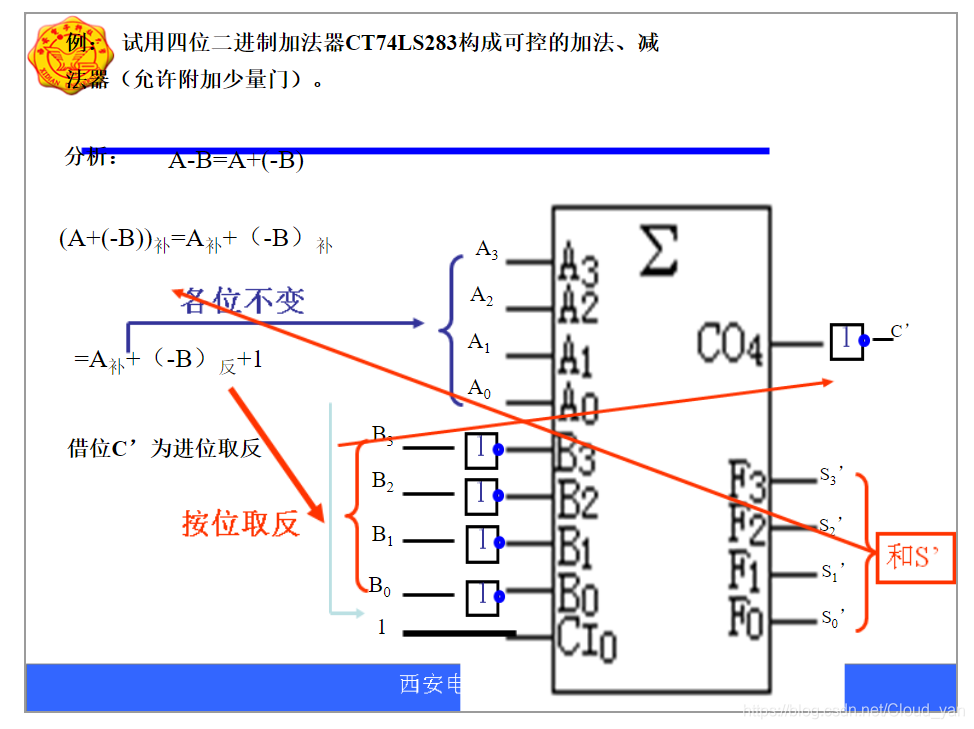

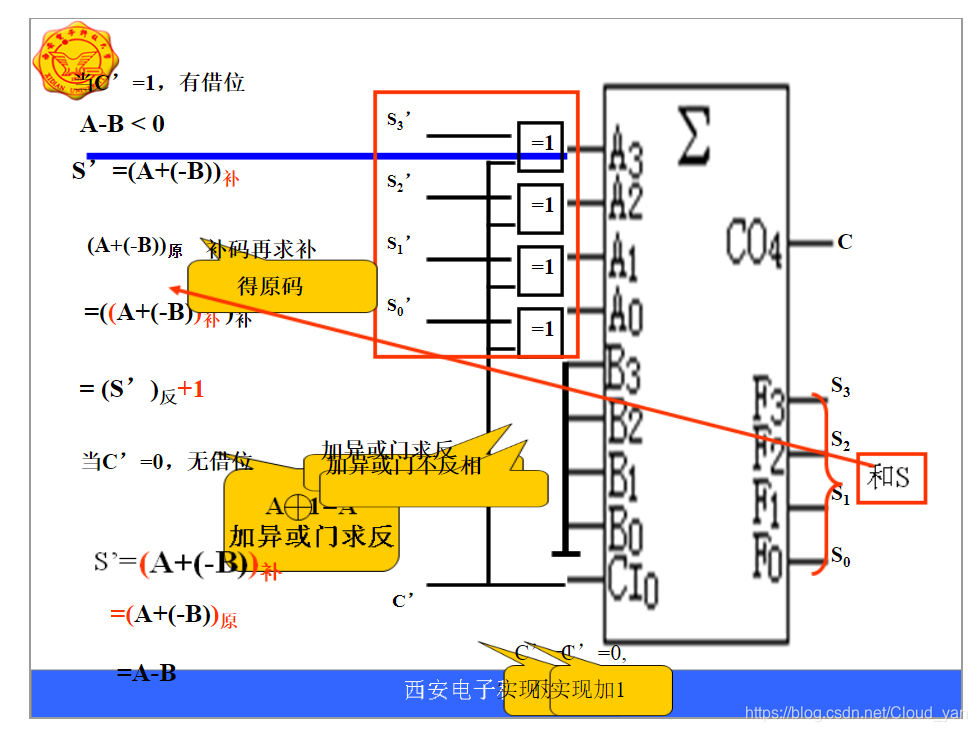

加法器的应用:

主要用于实现码组变换,加、减运算和乘法运算等。

P86页

实现一个余3码到8421BCD码的转换。

用一片74283实现F=2X+Y电路

下面是一个PPT,其内容挺好的。我给直接贴上来了。

组合电路中的竞争与冒险

由于逻辑门存在延迟时间以及信号的传输路径不同,当输入信号电平发生瞬间变化时,电路可能产生与稳态时逻辑功能不一致的错误输出,这种现象就是电路中的竞争与冒险。

毛刺由于发生跳变时,到达与非门的输入端有时间差,门电路有延迟,则会产生毛刺。

当某一输入变量发生变化时,由于传输路径不同,到达电路中某一个门的输入端的时间有先有后,这种时差现象称为竞争。

由于竞争而使电路输出端产生尖峰脉冲的现象称为冒险。

具有竞争的条件:存在多个传输路径,即有多个相同变量存在。例如:F=AB+ĀC,则A就具有竞争条件。

在一个输入变量发生变化的条件下,电路在过渡过程中产生的冒险一般称为逻辑冒险。

由于两个或多个输入变量变化时间不同步引起的冒险称为功能冒险。

冒险的判别:

- 代数法:若组合电路的输出函数为下列形式之一,则存在逻辑冒险现象。

F=A+Ā(存在0型冒险,负向毛刺)

F=A*Ā(存在1型冒险,正向毛刺) - 卡诺图法:若卡诺图中有两个卡诺圈相切,且相切处未被其他卡诺圈包围,则可能发生冒险现象。

冒险现象的消除:

- 增加冗余项消除逻辑冒险。冗余项本应消除,但为了保证电路工作可靠又需加上它。这证明了,最简化设计不一定是最佳的。

- 加滤波电路,消除毛刺影响。

- 加选通信号,避开毛刺。毛刺仅发生在输入信号变化的瞬间,因此在这段时间内先将门封住,待电路稳定后,再加选通脉冲选取输出结果。

三个方法的比较:

- 利用冗余项:只能消除逻辑冒险,而不能消除功能冒险;适

用范围有限。 - 加滤波电路:加滤波电容使输出信号变坏,引起波形的上升、下

降时间变长,不宜在中间级使用。实验调试阶段采用的应急

措施。 - 加选通信号:加取样脉冲对逻辑冒险及功能冒险都有效。目

前大多数中规模集成模块都设有使能端,可以将取样信

号作用于该端,待电路稳定后才使输出有效。