在使用MicroBlaze过程中,调用了此IP,所以有必须仔细学习下;

名词:

XIP: eXecute In Place

Motorola M68HC11

支持特性:

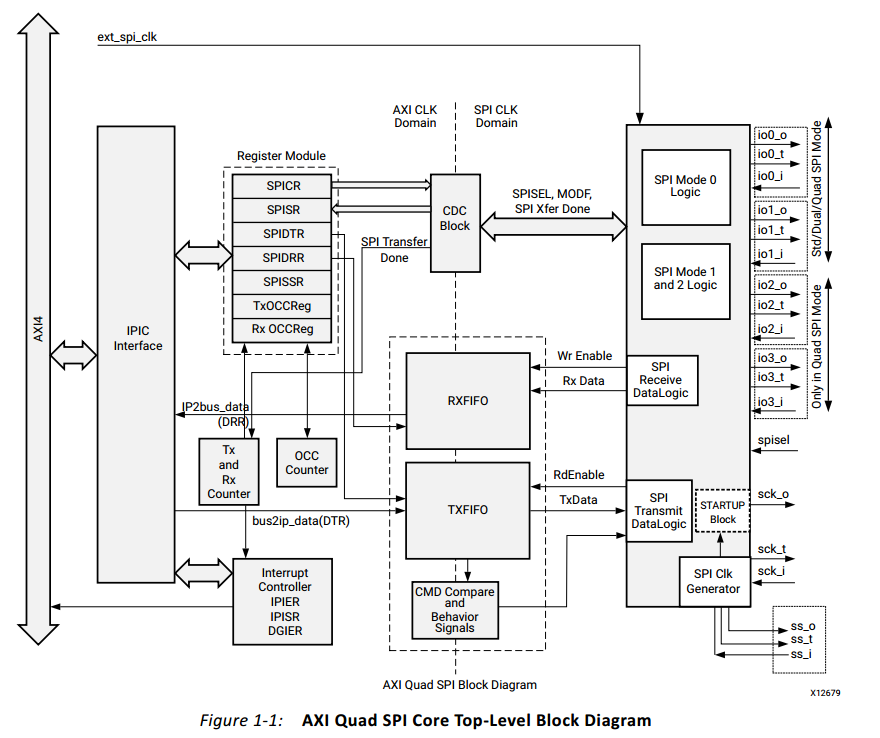

*可配置的AXI4接口

*支持对DRR/DTR FIFO的突发操作;

*支持可配置的XIP模式操作;

*支持AXI4-Lite或者AXI4接口连接的32bit Slave;

*支持可配置的SPI模式:标准、双、四模式;

*可编程的SPI时钟相位和极性;

*可配置的FIFO深度,16、256深度;对XIP模式只支持64深度;

*Configurable slave Memories in dual and quad modes are: Mixed,Micro,Winbond,and Spansion;

*AXI 接口选项:

XIP 模式: 使能AXI4 和 AXI4-Lite接口,地址模式可以选择24bit和32bit;

Performance 模式:使能AXI4接口;使用AXI4接口可以在核的发送和接收FIFO地址处启用突发功能。当不使能performance模式时,AXI4-Lite将被使用。

*SPI 选项

模式可以选择: standard/dual/quad

Transacton Width: 8/16/32

频率比率:2~2048, 代表了SPI的sck = ext_spi_clk/ratio ;

NO. of Slave: 代表了slave的个数;1~32;

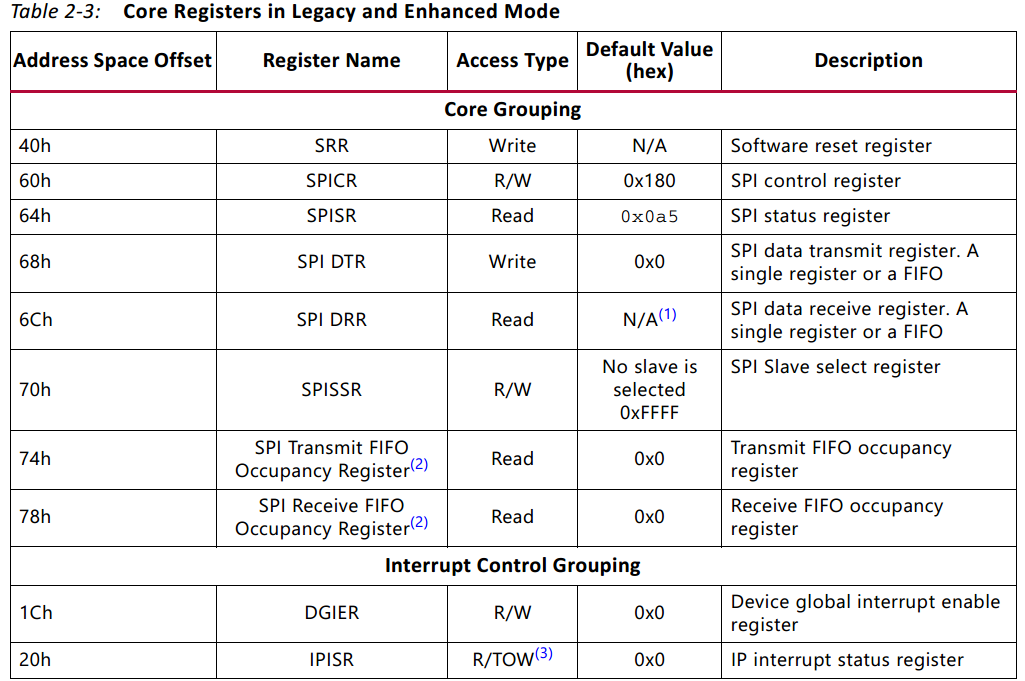

*寄存器:

AXI4-Lite写访问寄存器由32位AXI写数据(* _wdata)信号更新,不受AXI写数据选通(* _wstrb)信号的影响。对于写入,AXI写地址有效(* _awvalid)和AXI写数据有效(* _wvalid)信号需要同时有效。

表2-3显示了适用的寄存器集,无论是否使能Performance Mode,或禁止XIP模式。应单独访问某些AXI Quad SPI内核寄存器。这些寄存器是可配置的,可通过AXI4-Lite接口或AXI4接口(增强模式)访问。 所有寄存器都以32位的形式访问。

如果访问不存在的寄存器,它们将返回OKAY响应。 这些寄存器的读取返回0,写入没有任何影响。

*SPISRR: 写入0xA,进行软件复位;

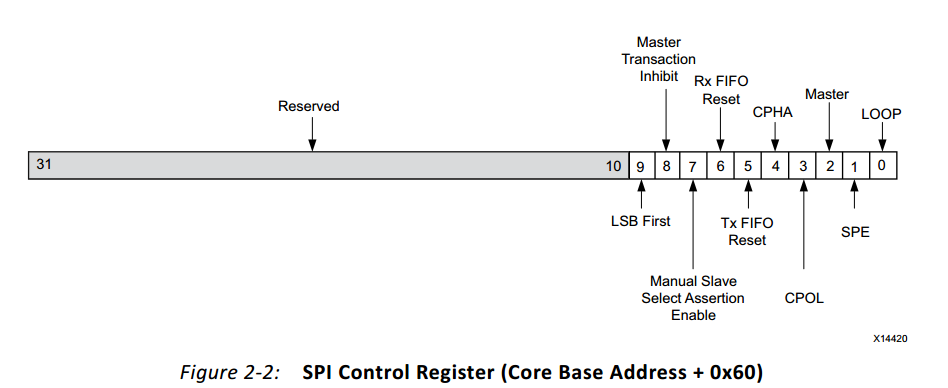

*SPICR

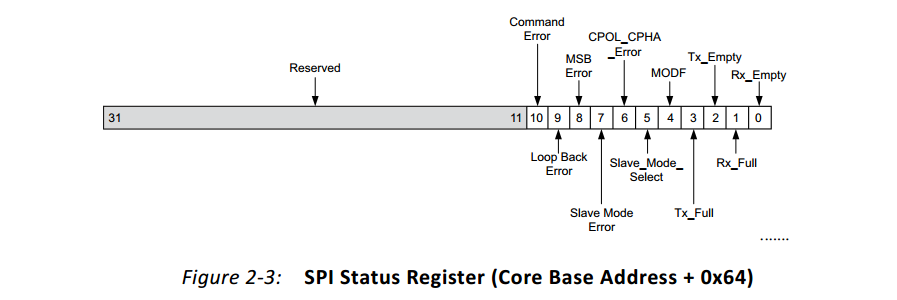

*SPISR

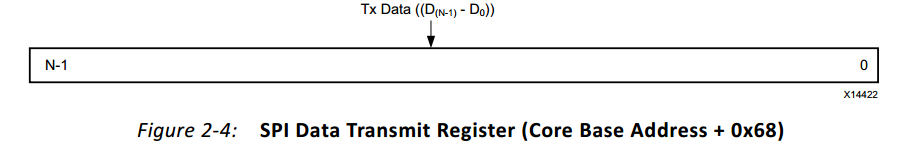

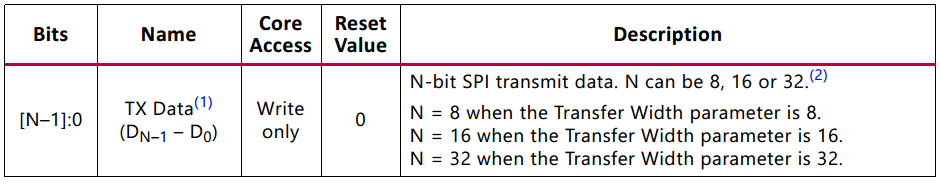

*SPI DTR:

After the SPE bit is set to 1 in master mode or spisel is active in the slave mode,the data is transferred from the SPI DTR to the shift register.

1. DN-1位始终表示MSB位,与LSB优先或MSB优先传输选择无关。 当传输宽度参数为8或16时,未使用的高位((AXI数据宽度-1)到N)被保留。

2.在标准SPI模式下,根据内核配置,该寄存器的宽度可以是8或16或32。 在双通道或四通道SPI模式下,该寄存器为8位宽。

* 编程顺序:

写使能命令顺序:

1.通过置位SPICR(60h)的主禁止位来禁用主事务,并通过SPICR复位RX和TX FIFO。

示例:将0x1E6写入SPICR

2.通过将0x06写入SPIDTR来发出write enable命令。

3.通过向SPISSR(70h)写入0x00来发出芯片选择。

4.通过置低SPICR主禁止位来使能主事务。

5.通过将0x01写入SPISSR来置低片选。

6.通过置位SPICR主禁止位来禁用主事务。

Erase Command Sequence

1. Reset RX and TX FIFOs through SPICR.

2. Issue sector erase command (a) into SPIDTR to erase any specific sector followed by the flash sector address or issue the bulk erase command (a) to erase the entire flash

followed by the flash base address.

Example: Write 0xD8 to SPIDTR

3. Issue chip select by writing 0x00 to SPISSR.

4. Enable master transaction by deasserting the SPICR master inhibit bit.

5. Deassert chip select by writing 0x01 to SPISSR.

6. Disable master transaction by asserting the SPICR master inhibit bit.

Write Data Command Sequence

1. Reset RX and TX FIFOs through SPICR.

2. Issue the write data command(a) (b) into SPIDTR, to write data into any specific sector

followed by the flash sector address.

3. Fill SPIDTR with the data to be written to flash; the maximum data size depends upon

the configured QSPI FIFO size.

4. Issue chip select by writing 0x00 to SPISSR.

5. Enable master transaction by deasserting the SPICR master inhibit bit.

6. Deassert chip select by writing 0x01 to SPISSR.

7. Disable master transaction by asserting the SPICR master inhibit bit.

Read Data Command Sequence

1. Reset RX and TX FIFOs through SPICR.

2. Issue the read data command (a) (b) into SPIDTR to read data from any specific sector

followed by the flash sector address.

3. Fill SPIDTR with the dummy data to read required data from the flash.

4. Issue chip select by writing 0x00 to SPISSR(70h).

5. Enable master transaction by deasserting the SPICR master inhibit bit.

6. Deassert chip select by writing 0x01 to SPISSR.

7. Disable master transaction by asserting SPICR master inhibit bit

8. Read SPIDRR, to get the Read data that is received from the SPI bus.

a.Refer to the respective SPI slave (flash) data sheet to know which commands to issue.

b.Write/Read commands vary with respect to the mode (Standard/Dual/Quad) used.