reference : ug470- 7 series config.pdf

7系列器件有5种配置接口,每种配置接口对应一种或者多种配置模式和总线位宽。配置时序相对于引脚的CCLK,即使在内部产生CCLK的主模式下也是如此。

Master模式包括: serial / spi / bpi / selectMAP ; JTAG模式 ; Slave模式包括:serial/selectMAP ;

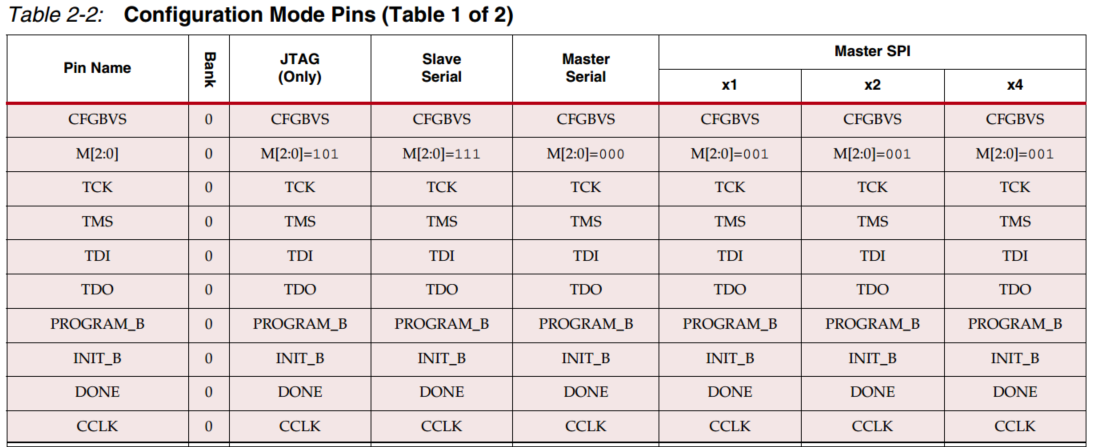

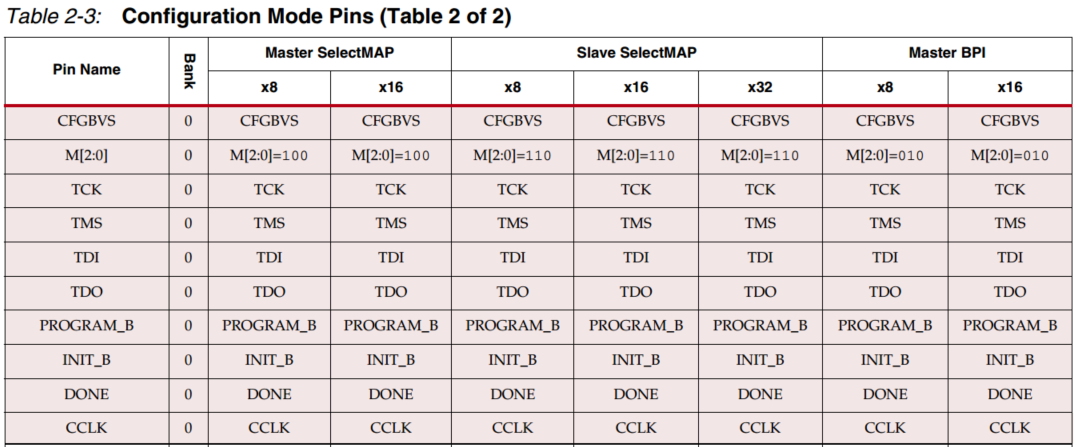

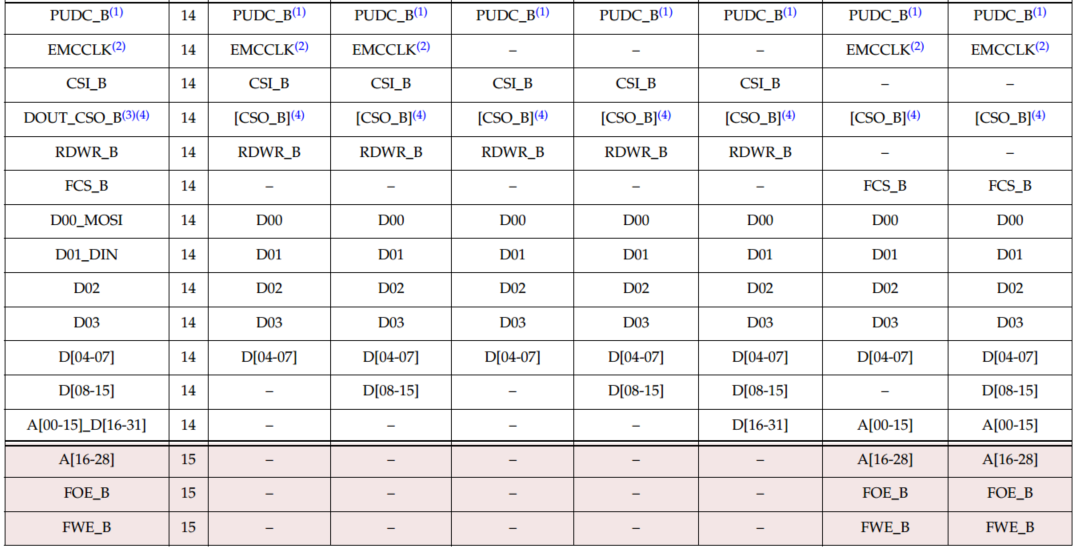

每种配置模式都有一组相应的接口引脚,跨越了7系列FPGA上的一个或多个I / O bank。 Bank 0包含专用配置引脚,始终是每个配置接口的一部分。 Bank 14和Bank 15包含涉及特定配置模式的多功能引脚。 在7系列FPGA数据手册中规定工作在3.3V,2.5V,1.8V或1.5V的bank中配置引脚的开关特性。

所有JTAG和专用配置引脚都位于一个独立的专用bank 0中,该bank具有专用电源(VCCO_0)。多功能引脚位于bank14和15中。

所有专用输入引脚均工作在VCCO_0 LVCMOS电平(LVCMOS18,LVCMOS25或LVCMOS33)。所有有源专用输出引脚均在VCCO_0电压电平下工作,输出标准设置为LVCMOS,12 mA驱动,快速摆率。对于使用多功能I / O的所有模式,必须将关联的VCCO_14或VCCO_15连接到适当的电压,以匹配配置器件的I / O标准。多功能引脚在配置时也是LVCMOS,12 mA驱动,快速摆率。 如果使用Persist选项,所选配置模式的多功能I / O,在配置后保持激活状态,I / O标准设置为LVCMOS的通用默认值,12 mA 驱动,慢摆率。

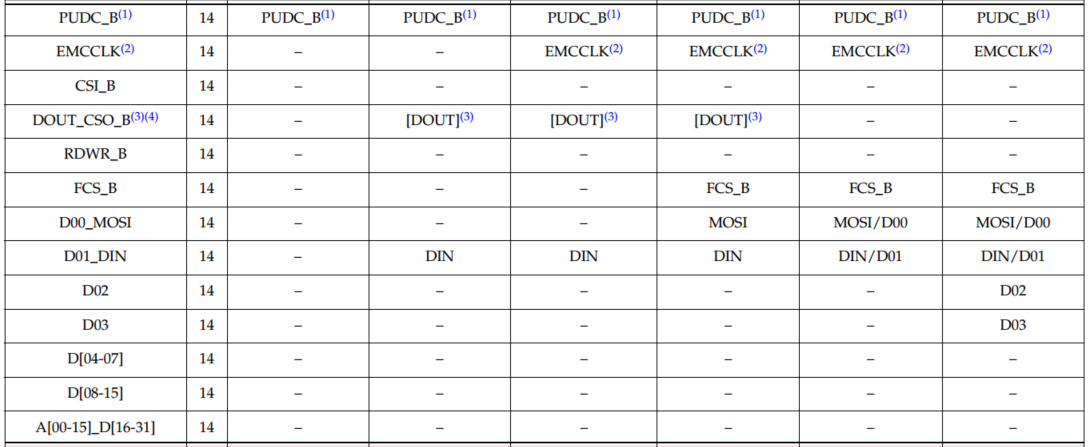

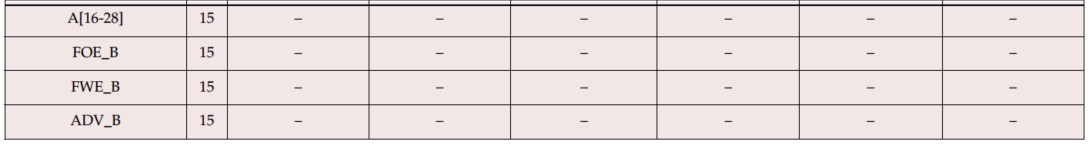

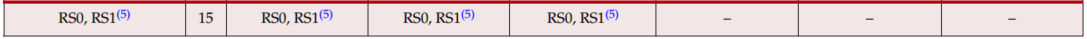

*配置模式引脚及其在I / O bank上的位置

注:

1. PUDC_B在配置期间具有特殊功能,但独立于所有配置接口,即PUDC_B不需要与配置接口中的其他引脚电压兼容。

2. EMCCLK仅在ExtMasterCclk_en选项启用EMCCLK作为主时钟配置模式的输入时使用。

3. DOUT仅用于串行配置菊花链,用于将数据输出到下游FPGA(或用于DebugBitstream选项)。 否则,DOUT为高阻抗。

4. CSO_B仅用于并行配置菊花链,用于向下游设备输出芯片使能信号。 否则,CSO_B为高Z.

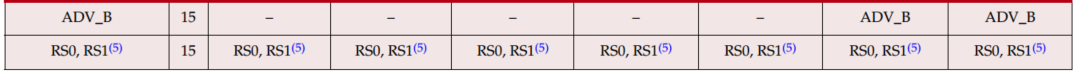

5. RS0和RS1仅在启动MultiBoot事件或启用ConfigFallback选项并发生Fallback事件时被驱动。否则,RS0和RS1为高阻态。 使用RS [1:0]引脚进行配置时,建议不要在用户模式下使用它们。

6. 空单元表示引脚未在配置模式下使用,并且在配置期间被忽略并且为高阻态。

*配置引脚定义

| 引脚名称 | bank | 类型 | 方向 | 描述 |

| CFGBVS | 0 | 专用 | 输入 | Configuration Banks Voltage Select VCCO0电压为3.3/2.5v时,CFGBVS为高电平,即接到VCCO0; VCCO0电压为1.8v时,CFGBVS为低电平,即接到GND。 |

| M[2:0] | 0 | 专用 | 输入 | Configuration Mode |

| TCK | 0 | 专用 | 输入 | JTAG Test Clock |