上一篇讲到了如何去运行xilinx给出的ddr3 ip sim example。这次来讲解一下如何通过自建的来仿真DDR3。

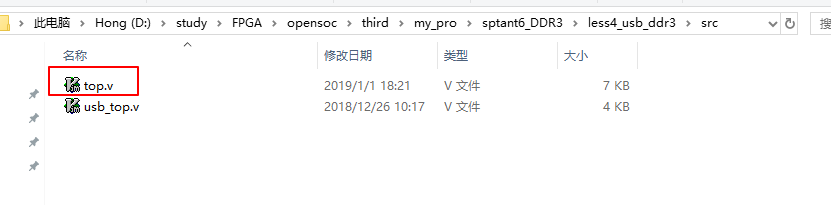

1.新建一个工程。新建一个top.v的文件。等会DDR3 Ip核例化在top中

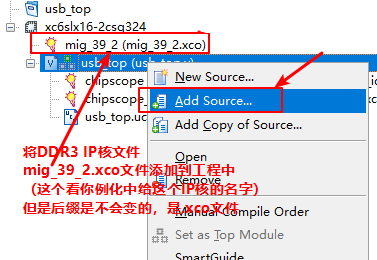

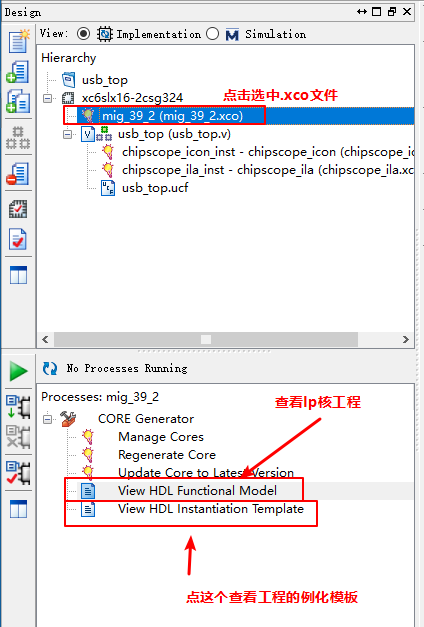

将DDR3 ip核添加到工程中,(.xco后缀的文件。)

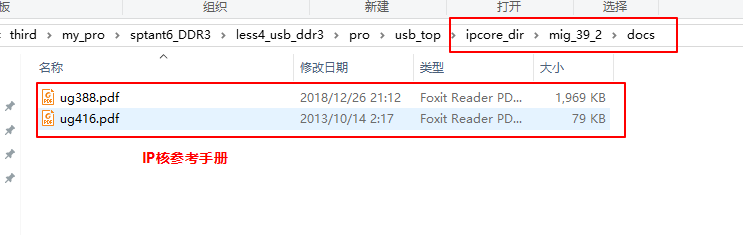

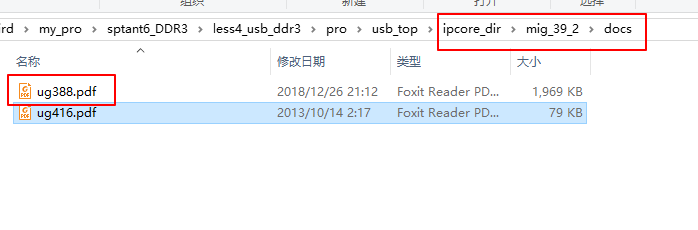

在生成的IPcore的docs文件夹里面有IP核需要参考的手册。

打开mig_39_2的例化模板

将DDR3 IP核例化到top文件中

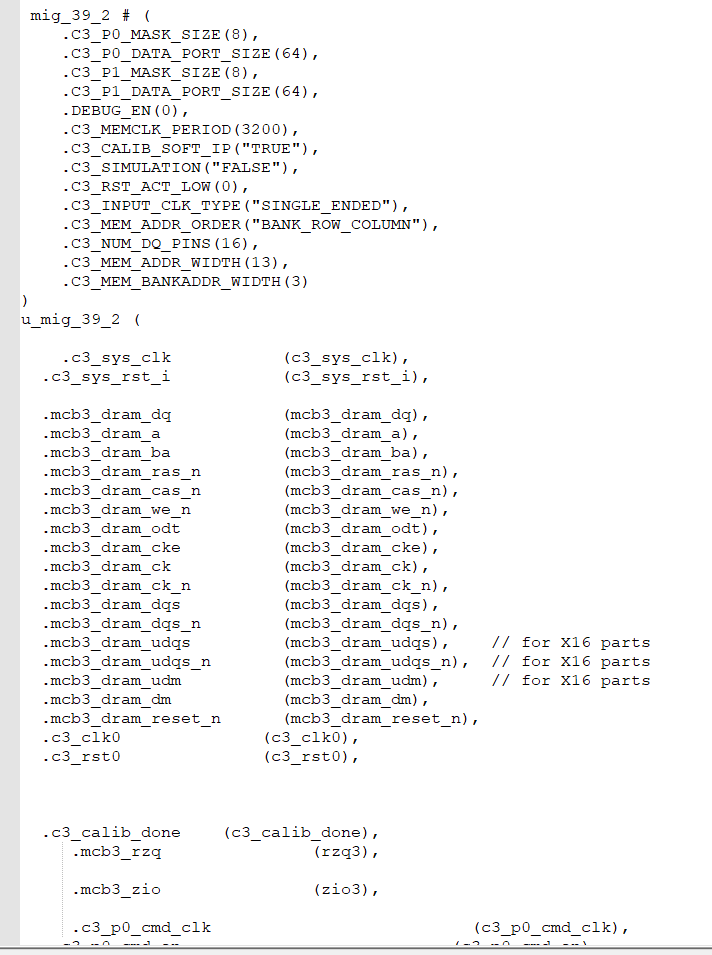

将这一大串内容复制到你的top文件中。

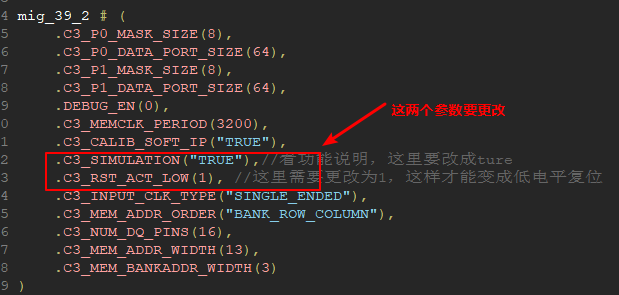

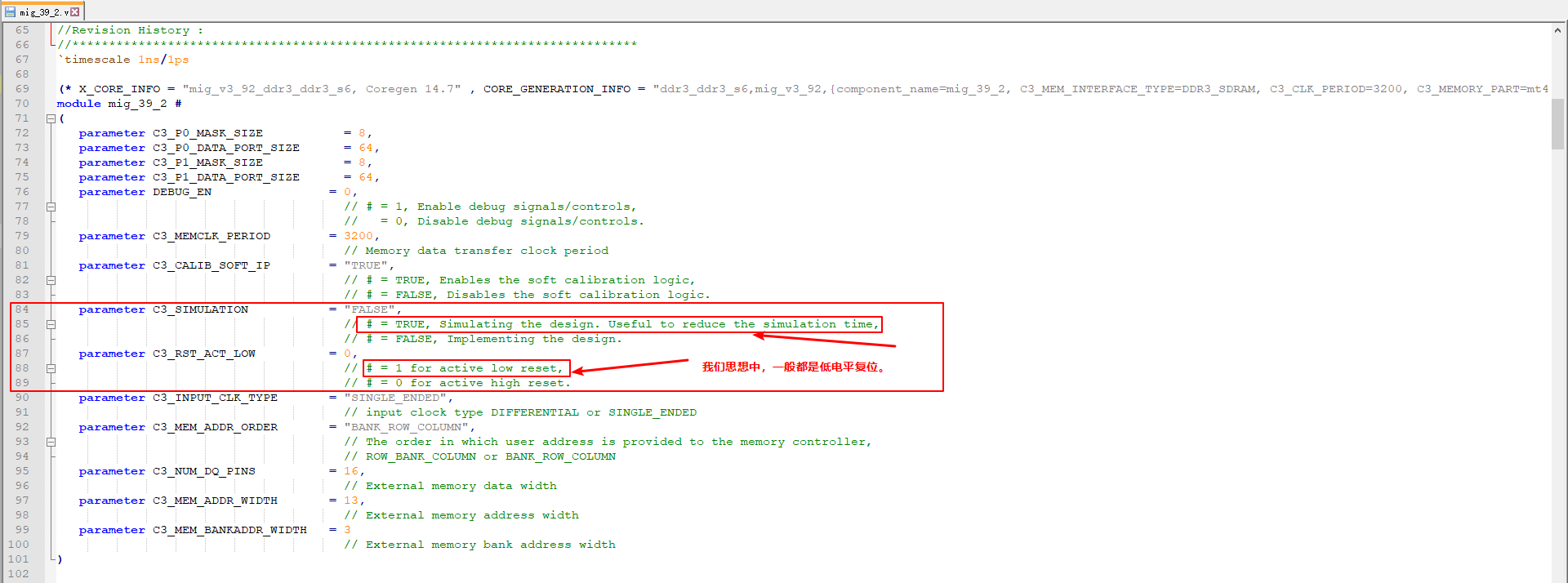

其中C3_SIMULATION和C3_RST_ACT_LOW这两个参数要更改。

这两个参数的作用:

C3_RST_ACT_LOW这个参数设置是高电平复位还是低电平复位。

C3_SIMULATION这个参数更改成TURE有利于仿真。

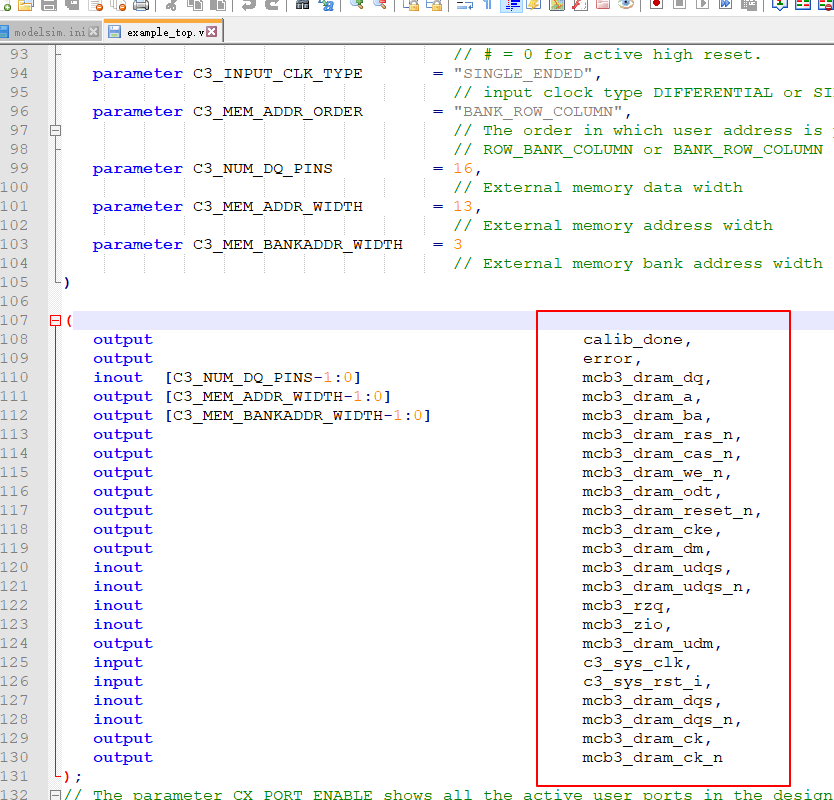

2.参考DDR3 IP的 example,打开example工程的顶层,我们模仿着他写

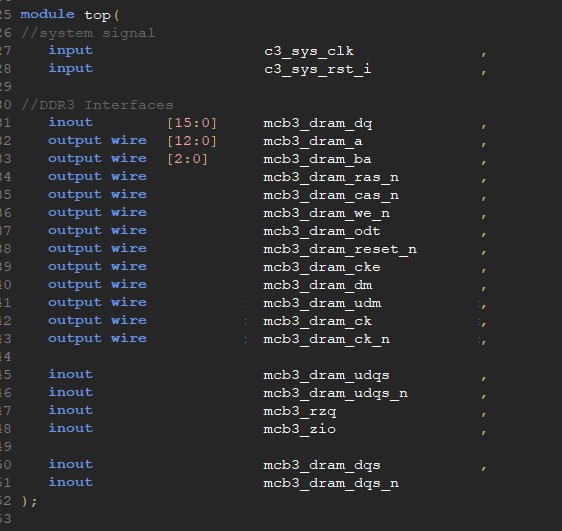

将这些信号添加到自己的工程top的module里面。

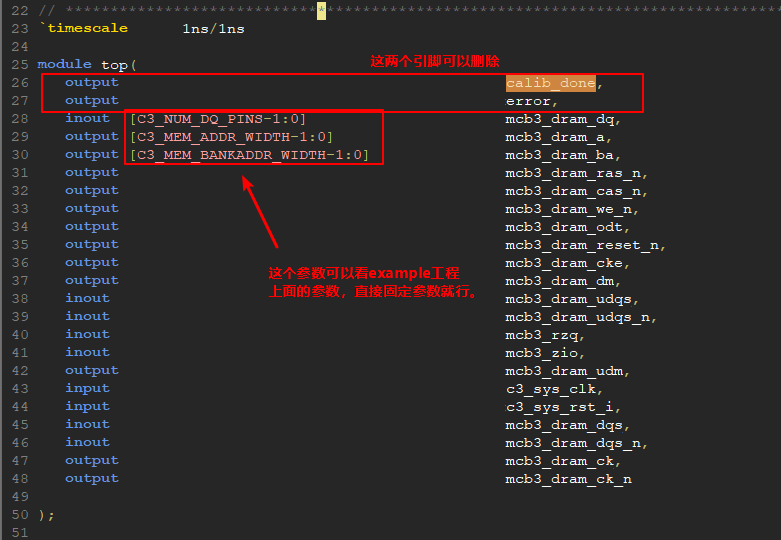

顶层信号中的calib_done在实际跑板子的时候是有作用的,因为这里只是作仿真,所以可以不要。

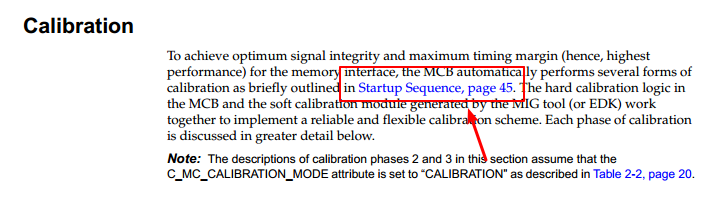

Calib_done信号作用,可以打开xilinx ip核的手册,在ip核目录下的doc文件夹中

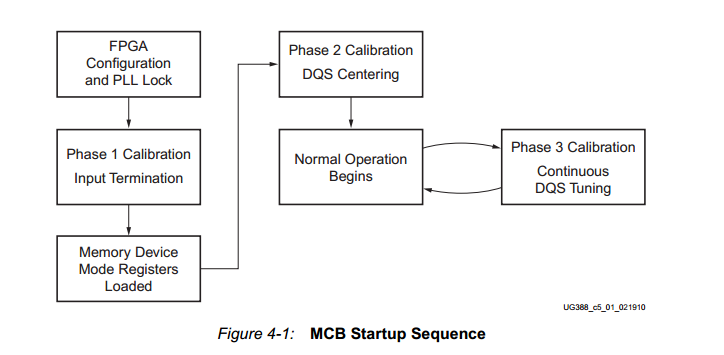

搜索calib_done,可以看到xilinx对他的介绍,可以知道calib_done是FPGA MCB初始化结束的标志信号,在他初始化的阶段,不能对DDR3进行读写操作。那FPGA MCB的初始化有哪些步骤呢?点击他的文本链接。

点击startup Sequence,page 45.

这个MCB的初始化操作步骤。

top中顶层信号最后的样子

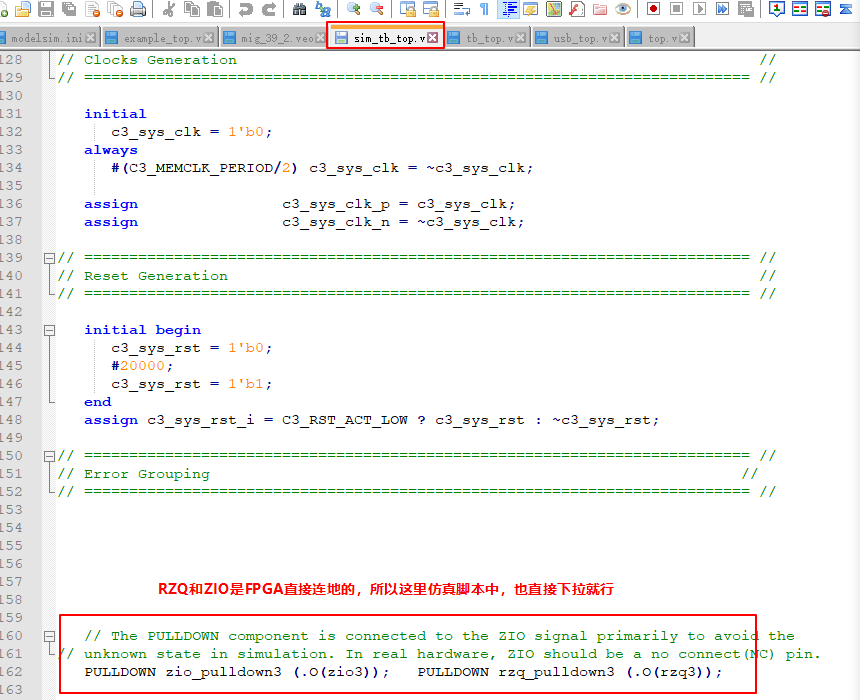

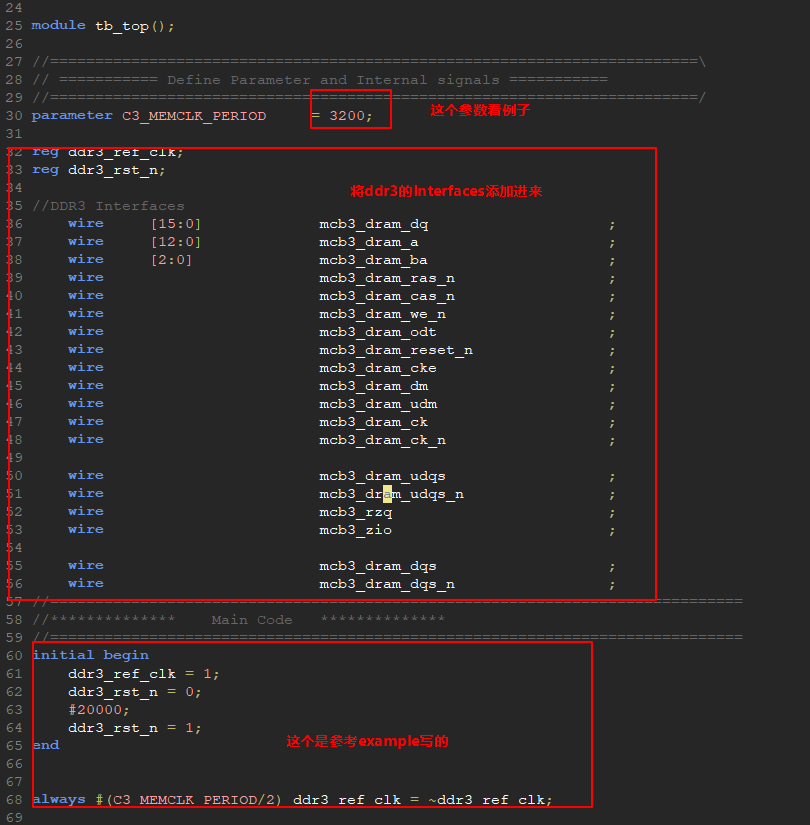

3.接下来编写sim仿真文件,还是和之前quartusii13一样,去模仿着example去做。先新建一个tb文件。

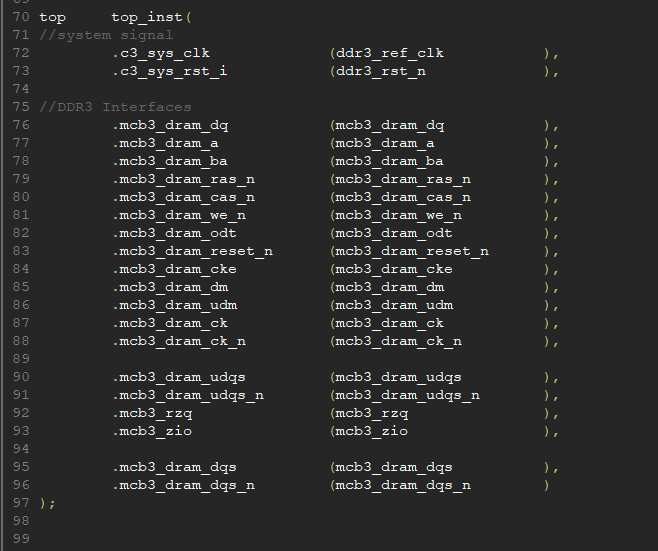

然后添加top例化到tb_top中。

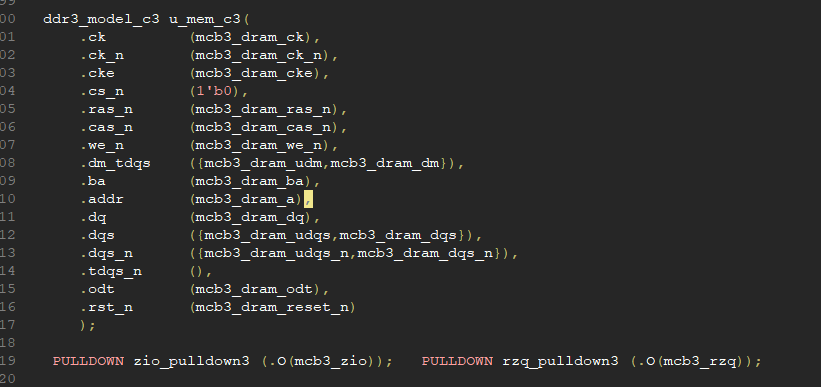

将DDR3的仿真模型和rzq和zio例化进去(这些也都是参考仿真例子的,req和zio都可以理解为一个校准信号,这是FPGA的信号,没有连接到DDR3中)

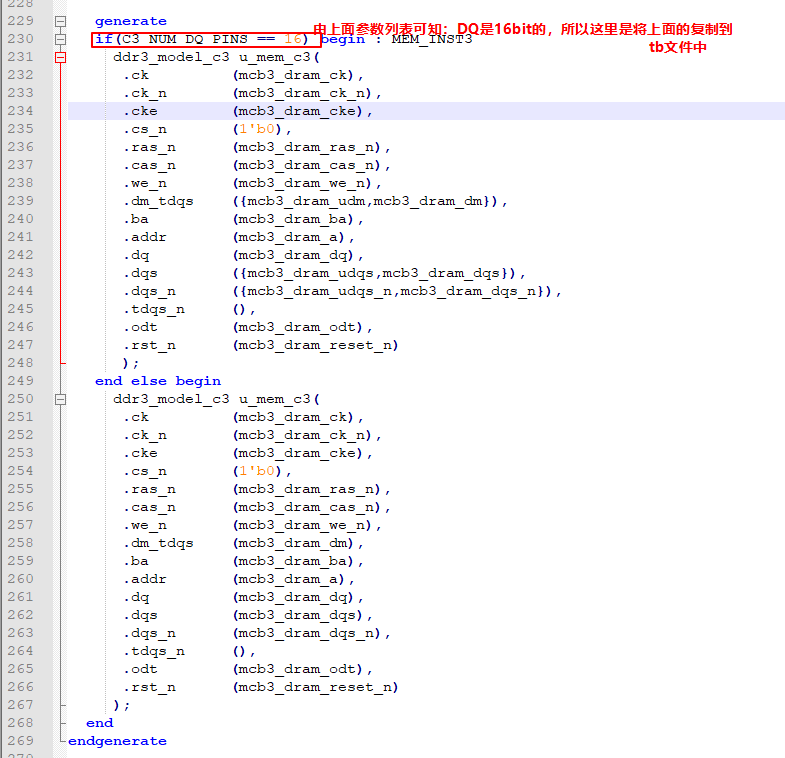

4.根据仿真脚本的提示,找到ddr3_model_c3这个文件。

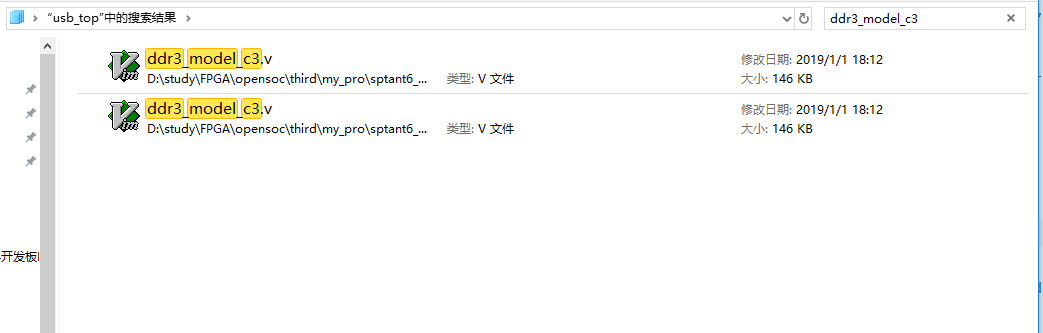

在工程中搜索这个文件,会有两个

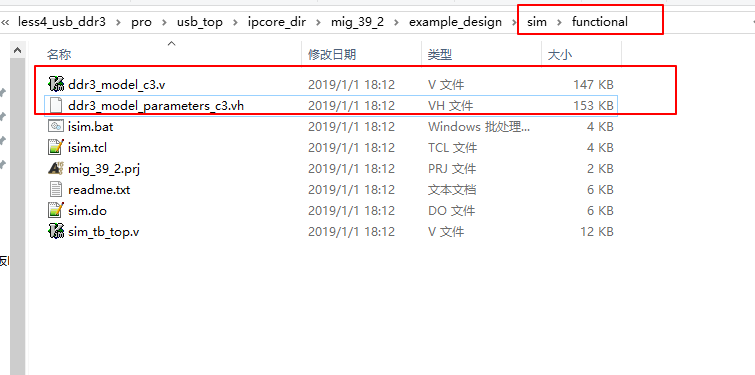

打开ddr3_model_c3.v可以知道,这个文件需要调用.vh的参数文件,所以要选择sim中functional文件夹的模型文件。

将ddr3_model_c3.v和 ddr3_model_parameters_c3.vh这两个文件复制到自己的sim文件夹下。(ddr3_model_parameters_c3.vh这个参数文件有些电脑是需要放在自己的ISE工程文件夹下才能运行的)

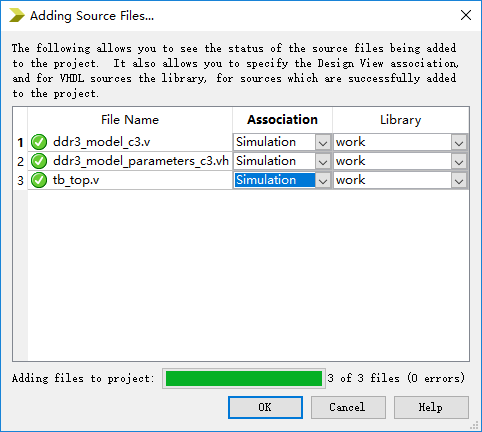

然后将sim下的tb_top和两个仿真模型文件添加到工程中

将属性改成sim。

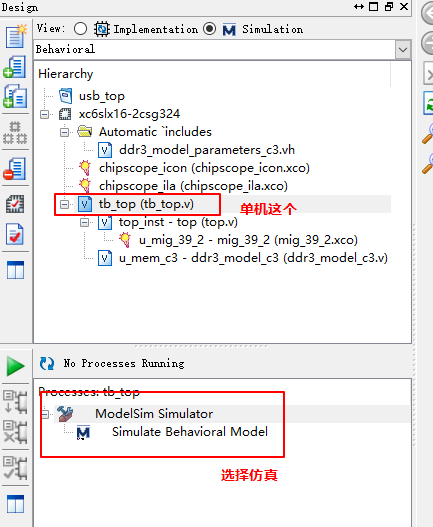

5.添加好后,点击tb_top可以进行仿真。

然后将top_inst添加到仿真波形中。

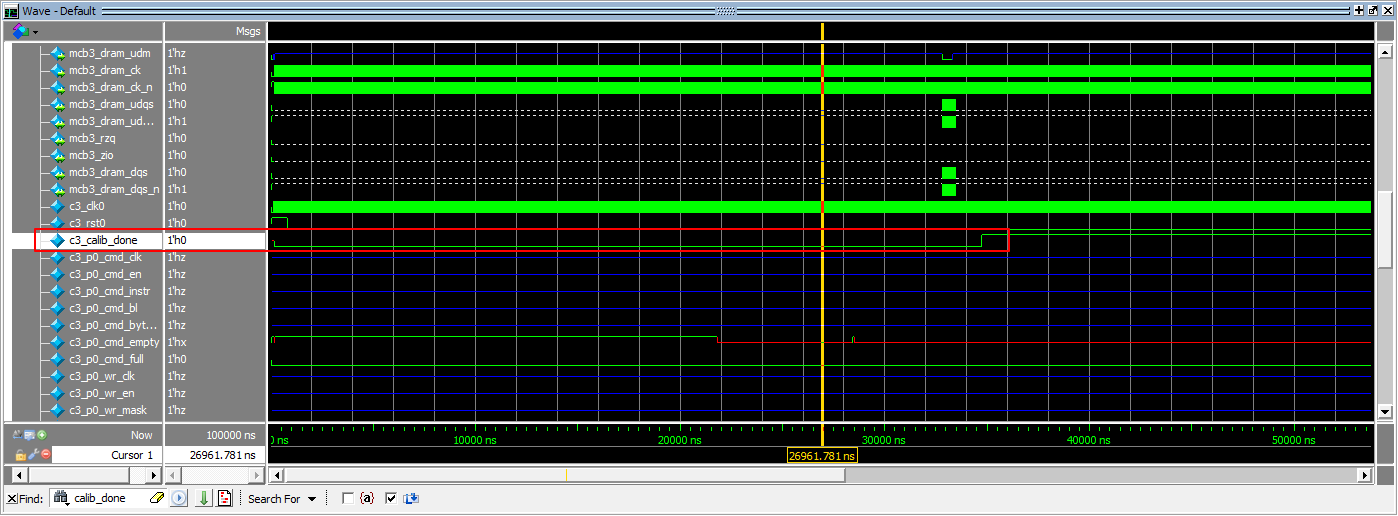

run个100us

去查看刚刚的calib_done这个信号有没有生成,如果有拉高,则说明自建平台搭建成功。