- 说在前面

开发环境:Vivado

语言:Verilog

cpu框架:Mips

控制器:组合逻辑

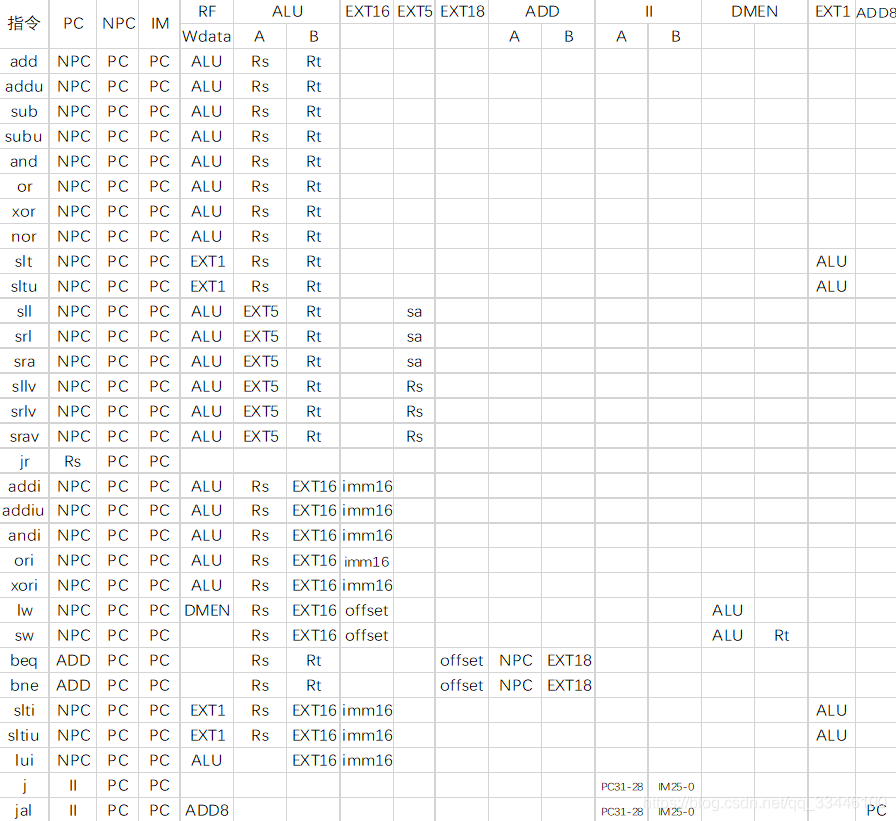

- 表格作用

这张表用于设计整体的数据通路图 (在第二篇中已经给出来了),而这张总图是用于设计Verilog代码整体结构的。

- 设计流程

在上一篇文章中分析了每一条指令的具体数据通路图 ,由于篇幅问题没有将单条指令的数据输入输出关系列举出来,所以就在这里整合一下(反正单条的数据通路图都有了)

步骤:

1. 将31条指令涉及到的所有部件作为表头,首列为指令

![]()

RF为寄存器堆;

2. 根据上一节内容,将每条指令各个部件的输入填入表格,未涉及的为空

NPC表示部件NPC的输出,其他同理;Rs\Rt为寄存器堆的两个输出

3. 得到表格

表中的imm16、offset等请根据指令的具体描述理解;

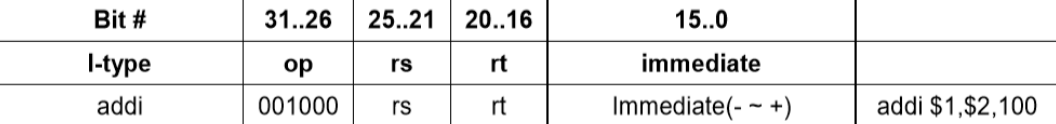

例如addi中的imm16,参考第二篇中:

又如lw中的offset:

![]()