前面我们介绍了使用双 FIFO 生成 3x3 矩阵的方法,并且对各种模式进行了推理和实验。本篇博客记录一下 Quartus II 软件下的 shift ip 核的使用方法。

要求:模拟一张分辨率为 10x5 的图片,图片的数据为 1~50,用 Verilog 对其生成 3x3 矩阵,以便后面的图像处理。

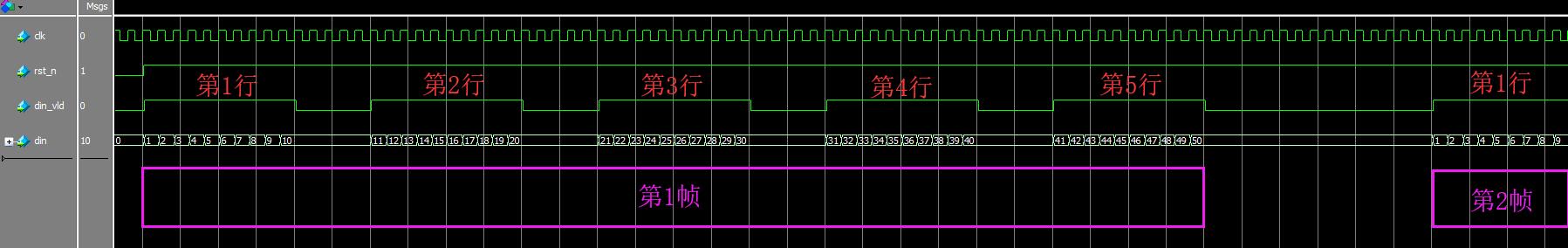

testbench:数据的使能和数据完美对齐,每隔 10 个数据就空闲小段时间,每隔 50 个数据又空闲一段时间,尽可能的模仿图像帧的样子,如下所示:

一、Shift IP 核原理解析

稍等

二、Shift IP 核调用

稍等

扫描二维码关注公众号,回复:

9557255 查看本文章

三、Shift IP 核生成 3x3 矩阵的仿真分析

稍等

四、实际上板

稍等