一、可编程逻辑设计

1、可编程逻辑设计流程图

①、模拟

先通过模拟器将设计进行仿真

②、综合

把高层次的描述转换成底层电路,形成网表

③、实现

将综合后的逻辑放置到一个逻辑器件之中的过程,同时实现合理布线

④、时序模拟

对设计的逻辑功能及时序进行验证

2、原理图输入

元件库:CAD工具提供一系列表示不同输入端数的各种类型门的图形符号

二、VHDL

1、语言结构

①、库

存放已经编译的实体、结构体、程序包、配置

②、程序包

存放各种设计模块能共享的数据类型、常数、程序等

③、实体

描述所设计硬件系统的外部接口信号

④、结构体

描述所设计硬件系统内部结构和功能

⑤、配置

用来从库中选取所需单元来组成新系统

(1)、实体格式

(2)、结构体格式

(3)、例:半加器

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

ENTITY half_adder IS

PORT ( A,B : IN std_logic;

Co : OUT std_logic;

S : OUT std_logic);

END half_adder;

ARCHITECTURE rtl OF half_adder IS

BEGIN

S <= A XOR B;

Co <= A AND B;

END rtl;

2、对象及数据类型

(1)、对象

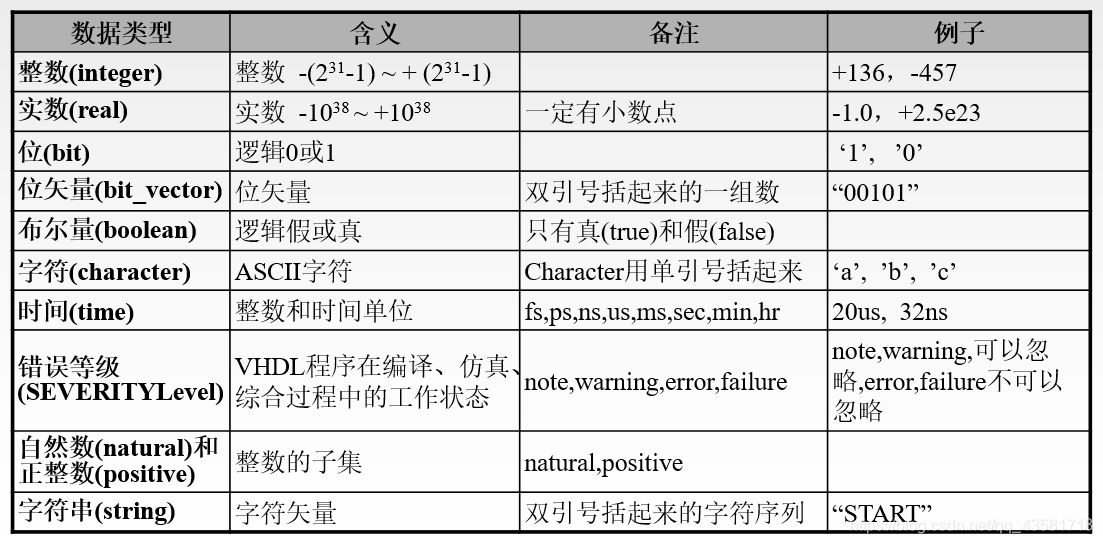

(2)、数据类型

①、标准数据类型

②、用户定义数据类型

原则:先定义,后使用

例:

可枚举类型std-logic定义:

3、并行描述语句

并行语句:描述一组并发行为,并发执行,与书写顺序无关

顺序语句:描述一组严格顺序执行的行为,与书写顺序有关

(1)、进程语句

一个结构体可以包括一个或多个进程语句,进程内部是顺序语句,各进程语句之间是并发行为

PROCESS [敏感信号表]

[进程语句说明部分] ;

BEGIN

<进程语句部分>;

END PROCESS

敏感信号的值发生改变,能够引起进程语句的执行

进程语句由顺序语句构成:IF语句、CASE语句、LOOP语句等

(2)、并发信号赋值语句

并发赋值语句在结构体中是并行执行的

例:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY gate IS

PORT (A,B : IN std_logic;

X,Y,Z : OUT std_logic);

END gate;

ARCHITECTURE behaveOF gate IS

BEGIN

X <= A AND B;

Y <= A OR B;

Z <= A XOR B;

END behave;

(3)、条件信号赋值语句

根据不同条件将不同的表达式赋值给目标信号

目标信号 <= 表达式1 when 条件1 else

表达式2 when 条件2 else

……

表达式n-1 when 条件n-1 else

表达式n;

例:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY and_gate IS

PORT (a,b : IN std_logic;

x : OUT std_logic);

END and_gate;

ARCHITECTURE rtl OF and_gate IS

BEGIN

x <= ‘0’ WHEN a=‘0’ AND b=‘0’ ELSE

‘0’ WHEN a=‘0’ AND b=‘1’ ELSE

‘0’ WHEN a=‘1’ AND b=‘0’ ELSE

‘1’;

END rtl;

(4)、选择信号赋值语句

with 表达式 select

目标信号 <=表达式1 when 选择条件1,

表达式2 when 选择条件2,

……

表达式n when 选择条件n,

例:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY mux4 IS

PORT (d0,d1,d2,d3 : IN std_logic;

sel: IN std_logic_vector(1 downto 0);

q : OUT std_logic);

END mux4;

ARCHITECTURE rtl OF mux4 IS

BEGIN

WITH sel SELECT

q <= d0 WHEN “00”,

d1 WHEN “01”,

d2 WHEN “10”,

d3 WHEN OTHER;

END rtl;

4、顺序描述语句

(1)、if语句

①

if 条件 then

顺序语句;

end if;

②

if 条件 then

顺序语句;

else

顺序语句;

end if;

③

if 条件1 then

第一组顺序语句;

elsif 条件2 then

第二组顺序语句;

……

elsif 条件n then

第n组顺序语句;

else

第n+1组顺序语句;

end if;

例:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY mux4 IS

PORT (d0 : IN std_logic_vector(3 DOWNTO 0);

d1 : IN std_logic_vector(3 DOWNTO 0);

d2 : IN std_logic_vector(3 DOWNTO 0);

d3 : IN std_logic_vector(3 DOWNTO 0);

sel : IN std_logic_vector(1 DOWNTO 0);

q : OUT std_logic_vector(3 DOWNTO 0));

END mux4;

ARCHITECTURE rtl OF mux4 IS

BEGIN

PROCESS(d0,d1,d2,d3,sel)

BEGIN

IF (sel = "00") THEN

q <= d0;

ELSIF (sel = "01") THEN

q <= d1;

ELSIF (sel = "10") THEN

q <= d2;

ELSE

q <= d3;

END IF;

END PROCESS;

END rtl;

(2)、case语句

case 条件表达式 is

when 条件表达式的值=>一组顺序语句;

……

when 条件表达式的值=>一组顺序语句;

end case;

例:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY mux4 IS

PORT (d0 : IN std_logic_vector(3 DOWNTO 0);

d1 : IN std_logic_vector(3 DOWNTO 0);

d2 : IN std_logic_vector(3 DOWNTO 0);

d3 : IN std_logic_vector(3 DOWNTO 0);

sel : IN std_logic_vector(1 DOWNTO 0);

q : OUT std_logic_vector(3 DOWNTO 0));

END mux4;

ARCHITECTURE rtl OF mux4 IS

BEGIN

PROCESS(d0,d1,d2,d3,sel)

BEGIN

CASE sel IS

WHEN "00" => q <= d0;

WHEN "01" => q <= d1;

WHEN "10" => q <= d2;

WHEN "11" => q <= d3;

WHEN OTHERS => q <= "ZZZZ";

END CASE;

END PROCESS;

END rtl;

(3)、loop语句

①、for loop语句:

循环标号:for 循环变量 in 范围 loop

顺序处理语句;

end loop 循环标号;

例:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY vector_to_int IS

PORT (input : IN std_logic_vector(7 DOWNTO 0);

flag : OUT boolean;

q : OUT integer);

END vector_to_int;

ARCHITECTURE behave OF vector_to_int IS

BEGIN

PROCESS(input)

VARIABLE tmp : integer := 0;

BEGIN

flag <= false;

FOR i IN 7 downto 0 LOOP

tmp := tmp * 2;

IF (input(i)= '1') THEN

tmp := tmp +1;

ELSIF (input(i)/= '0') THEN

flag <= true;

END IF;

END LOOP;

q <= tmp;

END PROCESS;

END behave;

②、while loop语句:

循环标号:while 条件表达式 loop

顺序处理语句;

end loop 循环标号;

例:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY logic_and IS

PORT (input : IN std_logic_vector(7 DOWNTO 0);

q : OUT std_logic);

END logic_and;

ARCHITECTURE behave OF logic_and IS

BEGIN

PROCESS(input)

VARIABLE tmp : std_logic;

VARIABLE i : integer;

BEGIN

tmp := '1';

i := 0;

WHILE (i<8) LOOP

tmp := tmp AND input(i);

i :=i+1;

END LOOP;

q <= tmp;

END PROCESS;

END behave;

5、结构体的三种描述方式

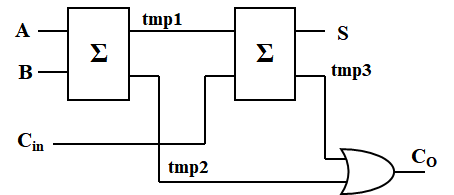

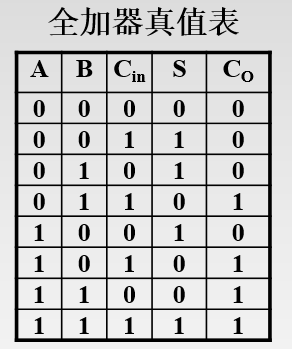

设计全加器

(1)、数据流描述方式

描述从输入到输出信号的走向

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY full_adder IS

PORT (A,B : IN std_logic;

Cin : IN std_logic;

Co : OUT std_logic;

S : OUT std_logic);

END full_adder;

ARCHITECTURE rtl OF full_adder IS

SIGNAL tmp1,tmp2 : std_logic;

BEGIN

tmp1 <= A XOR B;

tmp2 <= tmp1 AND Cin;

S <= tmp1 XOR Cin;

Co <= tmp2 OR (A AND B);

END rtl;

(2)、结构描述方式

通过调用库中的元件或是已设计好的模块来完成设计实体功能的描述

半加器:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY half_adder IS

PORT ( A,B : IN std_logic;

Co : OUT std_logic;

S : OUT std_logic);

END half_adder;

ARCHITECTURE rtl OF half_adder IS

SIGNAL tmp1,tmp2 : std_logic;

BEGIN

tmp1 <= A OR B;

tmp2 <= A NAND B;

Co <= NOT tmp2;

S <= tmp1 AND tmp2;

END rtl;

全加器:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY full_adder IS

PORT (A,B : IN std_logic;

Cin : IN std_logic;

Co : OUT std_logic;

S : OUT std_logic);

END full_adder;

ARCHITECTURE structure OF full_adder IS

SIGNAL tmp1,tmp2,tmp3 : std_logic;

COMPONENT half_adder

PORT(A,B : IN std_logic;

Co : OUT std_logic;

S : OUT std_logic);

END COMPONENT;

COMPONENT or_gate

PORT(a,b : IN std_logic;

c : OUT std_logic);

END COMPONENT;

BEGIN

U0: half_adder

PORT MAP (A=>A,B=>B, S=>tmp1,Co=>tmp2);

U1: half_adder

PORT MAP (A=>tmp1,B=>Cin,S=>S, Co=>tmp3);

U2: or_gate

PORT MAP (a=>tmp3,b=>tmp2,c=>Co);

END structure;

COMPONENT调用已有组件

PORT MAP将设计的端口名称替换为被调用组件的端口名称

(3)、行为描述方式

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY full_adder IS

PORT (A,B, Cin : IN std_logic;

Co, S : OUT std_logic;

END full_adder;

ARCHITECTURE behave OF full_adder IS

BEGIN

PROCESS(A,B,Cin)

VARIABLE n : integer RANGE 0 TO 3;

CONSTANT S_vector : std_logic_vector(0 TO 3) :="0101";

CONSTANT Co_vector : std_logic_vector(0 TO 3) :="0011";

BEGIN

n := 0;

IF (A ='1') THEN

n := n+1;

END IF;

IF (B ='1') THEN

n := n+1;

END IF;

IF (Cin ='1') THEN

n := n+1;

END IF;

S <= S_vector(n);

Co <= Co_vector(n);

END PROCESS;

END behave;

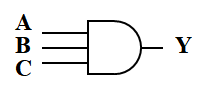

6、VHDL的组合逻辑设计

(1)、多输入简单门电路

例:三输入与门

①

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY and3_gate IS

PORT (a,b,c : IN std_logic;

y : OUT std_logic);

END and3_gate;

ARCHITECTURE behave_arc OF and3_gate IS

BEGIN

PROCESS(a,b,c)

BEGIN

y <= a AND b AND c;

END PROCESS;

END behave_arc;

②

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY and3_gate IS

PORT (a,b,c : IN std_logic;

y : OUT std_logic);

END and3_gate;

ARCHITECTURE rtl_arc OF and3_gate IS

BEGIN

PROCESS (a,b,c)

VARIABLE comb : std_logic_vector(2 DOWNTO 0);

BEGIN

comb := a & b & c;

CASE comb IS

WHEN "000" => y <= '0';

WHEN "001" => y <= '0';

WHEN "010" => y <= '0';

WHEN "011" => y <= '0';

WHEN "100" => y <= '0';

WHEN "101" => y <= '0';

WHEN "110" => y <= '0';

WHEN "111" => y <= '1';

WHEN OTHERS => y <= 'X';

END CASE;

END PROCESS;

END rtl_arc;

&:并置运算符,将逻辑信号连接后形成一个新的位矢量

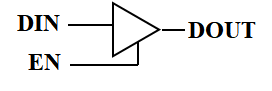

(2)、三态门电路

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY tri_gate IS

PORT (din,en : IN std_logic;

dout : OUT std_logic);

END tri_gate;

ARCHITECTURE behave_arc OF tri_gate IS

BEGIN

PROCESS (din,en)

BEGIN

IF (en = '1') THEN

dout <= din;

ELSE

dout <= 'Z';

END IF;

END PROCESS;

END behave_arc;

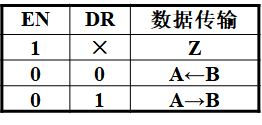

(3)、总线缓冲器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY bidir_bus_buff8 IS

PORT (a,b : INOUT std_logic_vector(7 DOWNTO 0);

en,dr : IN std_logic;

END bidir_bus_buff8;

ARCHITECTURE rtl_arc OF bidir_bus_buff8 IS

SIGNAL aout,bout : std_logic_vector(7 DOWNTO 0);

BEGIN

PROCESS (a,b,dr,en)

BEGIN

IF (en = '0' AND dr = '1') THEN

bout <= a;

ELSIF (en = '0' AND dr = '0') THEN

aout <= b;

ELSE

aout <= "ZZZZZZZZ";

bout <= "ZZZZZZZZ";

END IF;

b <= bout;

a <= aout;

END PROCESS;

END rtl_arc;

(4)、选择器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY mux IS

PORT (a,b,c,d: IN std_logic;

s: IN std_logic_vector(1 downto 0);

y: OUT std_logic);

END mux;

ARCHITECTURE rtl OF mux IS

BEGIN

y <= a WHEN s=“00” ELSE

b WHEN s=“01” ELSE

c WHEN s=“10” ELSE

d WHEN s=“11” ELSE

‘X’;

END rtl;

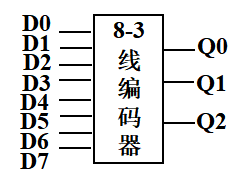

(5)、编码器

①、普通编码器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY encoder8_3 IS

PORT (d : IN std_logic_vector(0 TO 7);

q : OUT std_logic_vector(2 DOWNTO 0));

END encoder8_3;

ARCHITECTURE rtl_arc OF encoder8_3 IS

BEGIN

PROCESS (d)

BEGIN

CASE d IS

WHEN "01111111" => q <= "111";

WHEN "10111111" => q <= "110";

WHEN "11011111" => q <= "101";

WHEN "11101111" => q <= "100";

WHEN "11110111" => q <= "011";

WHEN "11111011" => q <= "010";

WHEN "11111101" => q <= "001";

WHEN "11111110" => q <= "000";

WHEN OTHERS => q <= "ZZZ";

END CASE;

END PROCESS;

END rtl_arc;

②、优先编码器

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY BIM IS

PORT (st : IN STD_LOGIC;

d : IN STD_LOGIC_VECTOR(0 TO 7);

ye,ys : OUT STD_LOGIC;

y : OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END BIM;

ARCHITECTURE func OF BIM IS

BEGIN

PROCESS (st,d)

BEGIN

IF (st='0') THEN

IF d(7)='0' THEN y<="000";ye<='0';ys<='1';

ELSIF d(6)='0' THEN y<="001";ye<='0';ys<='1';

ELSIF d(5)='0' THEN y<="010";ye<='0';ys<='1';

ELSIF d(4)='0' THEN y<="011";ye<='0';ys<='1';

ELSIF d(3)='0' THEN y<="100";ye<='0';ys<='1';

ELSIF d(2)='0' THEN y<="101";ye<='0';ys<='1';

ELSIF d(1)='0' THEN y<="110";ye<='0';ys<='1';

ELSIF d(0)='0' THEN y<="111";ye<='0';ys<='1';

ELSE y<="111";ye<='1';ys<='0';

END IF;

ELSE

y <= "111";ye<='1';ys<='1';

END IF;

END PROCESS;

END func;

(6)、译码器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY decoder_74LS138 IS

PORT (g1,g2a,g2b,a,b,c : IN std_logic;

y : OUT std_logic_vector(7 DOWNTO 0));

END decoder_74LS138;

ARCHITECTURE rtl_arc OF decoder_74LS138 IS

SIGNAL comb : std_logic_vector(2 DOWNTO 0);

BEGIN

comb <= c & b & a;

PROCESS (g1,g2a,g2b,comb)

BEGIN

IF (g1 = '1' AND g2a = '0' AND g2b = '0') THEN

CASE comb IS

WHEN "000" => y <= "11111110";

WHEN "001" => y <= "11111101";

WHEN "010" => y <= "11111011";

WHEN "011" => y <= "11110111";

WHEN "100" => y <= "11101111";

WHEN "101" => y <= "11011111";

WHEN "110" => y <= "10111111";

WHEN "111" => y <= "01111111";

WHEN OTHERS => y <= "XXXXXXXX";

END CASE;

ELSE

y <= "11111111";

END IF;

END PROCESS;

END rtl_arc;

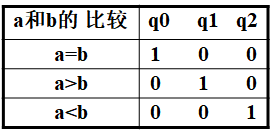

(7)、比较器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY comparison IS

PORT (a : IN std_logic;

b : IN std_logic;

q : OUT std_logic_vector(2 DOWNTO 0));

END comparison;

ARCHITECTURE behave_arc OF comparison IS

BEGIN

PROCESS (a,b)

BEGIN

IF (a = b) THEN

q <= "001";

ELSIF (a > b) THEN

q <= "010";

ELSE

q <= "100";

END IF;

END PROCESS;

END behave_arc;

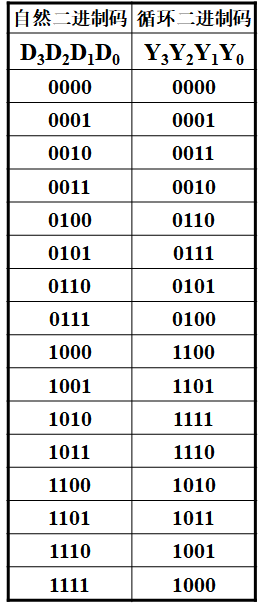

(8)、转换器

Y0=D0⊕D1

Y1=D1⊕D2

Y2=D2⊕D3

Y3=D3

library IEEE;

use IEEE.std_logic_1164.all;

entity BIN2GARY is

port ( DATA_IN : in std_logic_vector (3 downto 0);

EN : in std_logic;

DATA_OUT : out std_logic_vector (3 downto 0) );

end entity;

architecture bin2gary_arch of BIN2GARY is

begin

DATA_OUT(0) <= (DATA_IN(0) xor DATA_IN(1)) and EN;

DATA_OUT(1) <= (DATA_IN(1) xor DATA_IN(2)) and EN;

DATA_OUT(2) <= (DATA_IN(2) xor DATA_IN(3)) and EN;

DATA_OUT(3) <= DATA_IN(3) and EN;

end architecture;

7、VHDL时序逻辑设计

时钟信号:描述时序电路执行的条件

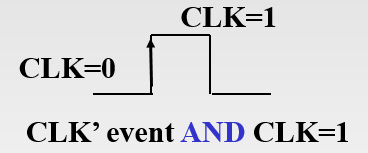

①、上升沿有效

也可以描述为:

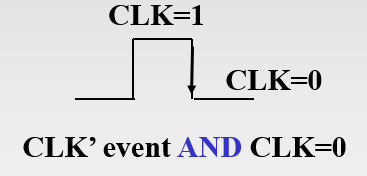

②、下降沿有效

也可以描述为:

③、同步复位/置位信号

用来设置时序电路的初始状态

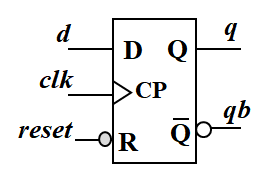

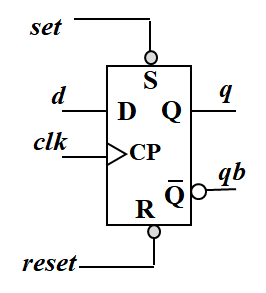

(1)、触发器

①、基本D触发器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY basic_dff IS

PORT (d,clk : IN std_logic;

q,qb : OUT std_logic);

END basic_dff;

ARCHITECTURE rtl_arc OF basic_dff IS

BEGIN

PROCESS (clk)

BEGIN

IF (clk'event AND clk ='1') THEN

q <= d;

qb <= NOT d;

END IF;

END PROCESS;

END rtl_arc;

②、同步复位D触发器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY sync_rdff IS

PORT (d,clk, reset : IN std_logic;

q,qb: OUT std_logic);

END sync_rdff;

ARCHITECTURE rtl_arc OF sync_rdff IS

BEGIN

PROCESS (clk)

BEGIN

IF (clk'event AND clk ='1') THEN

IF (reset :='0') THEN

q <= '0';

qb <= '1';

ELSE

q <= d;

qb <= NOT d;

END IF;

END IF;

END PROCESS;

END rtl_arc;

③、异步复位D触发器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY sync_rdff IS

PORT (d,clk, reset : IN std_logic;

q,qb: OUT std_logic);

END sync_rdff;

ARCHITECTURE rtl_arc OF sync_rdff IS

BEGIN

PROCESS (clk,reset)

BEGIN

IF (reset :='0') THEN

q <= '0';

qb <= '1';

ELSIF (clk'event AND clk ='1') THEN

q <= d;

qb <= NOT d;

END IF;

END PROCESS;

END rtl_arc;

④、同步置位/复位D触发器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY sync_rsdff IS

PORT (d,clk,set,reset: IN std_logic;

q,qb: OUT std_logic);

END sync_rsdff;

ARCHITECTURE rtl_arc OF sync_rsdff IS

BEGIN

PROCESS (clk)

BEGIN

IF (clk'event AND clk ='1') THEN

IF (set ='0' AND reset ='1') THEN

q <= '1';

qb <= '0';

ELSIF (set ='1' AND reset ='0') THEN

q <= '0';

qb <= '1';

ELSE

q <= d;

qb <= NOT d;

END IF;

END IF;

END PROCESS;

END rtl_arc;

⑤、异步置位/复位D触发器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY async_rsdff IS

PORT (d,clk,set,reset: IN std_logic;

q,qb: OUT std_logic);

END async_rsdff;

ARCHITECTURE rtl_arc OF async_rsdff IS

BEGIN

PROCESS (clk,set,reset)

BEGIN

IF (set ='0' AND reset ='1') THEN

q <= '1';

qb <= '0';

ELSIF (set ='1' AND reset ='0') THEN

q <= '0';

qb <= '1';

ELSIF (clk'event AND clk ='1') THEN

q <= d;

qb <= NOT d;

END IF;

END PROCESS;

END rtl_arc;

⑥、异步置位/复位JK触发器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY async_rsjkff IS

PORT (j,k,clk,set,reset: IN std_logic;

q,qb: OUT std_logic);

END async_rsjkff;

ARCHITECTURE rtl_arc OF async_rsjkff IS

SIGNAL q_temp,qb_temp : std_logic;

BEGIN

PROCESS (clk,set,reset)

BEGIN

IF (set ='0' AND reset ='1') THEN

q_temp <= '1';

qb_temp <= '0';

ELSIF (set ='1' AND reset ='0') THEN

q_temp <= '0';

qb_temp <= '1';

ELSIF (clk'event AND clk ='1') THEN

IF (j ='0' AND k ='1') THEN

q_temp <= '0';

qb_temp <= '1';

ELSIF (j ='1' AND k ='0') THEN

q_temp <= '1';

qb_temp <= '0';

ELSIF (j ='1' AND k ='1') THEN

q_temp <= NOT q_temp;

qb_temp <= NOT qb_temp;

END IF;

END IF;

q <= q_temp;

qb <= qb_temp;

END PROCESS;

END rtl_arc;

(2)、锁存器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY latch_74LS373 IS

PORT (d: IN std_logic_vector(7 DOWNTO 0);

oe,g: IN std_logic;

q: INOUT std_logic_vector(7 DOWNTO 0));

END latch_74LS373;

ARCHITECTURE rtl_arc OF latch_74LS373 IS

BEGIN

PROCESS (oe,g)

BEGIN

IF (oe ='0') THEN

IF (g ='1') THEN

q <= d;

ELSE

q <= q;

END IF;

ELSE

q <= "ZZZZZZZZ";

END IF;

END PROCESS;

END rtl_arc;

(3)、寄存器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY registerN IS

GENERIC (n: integer :=8);

PORT (d: IN std_logic_vector(n-1 DOWNTO 0);

en: IN std_logic;

clk: IN std_logic;

q: BUFFER std_logic_vector(n-1 DOWNTO 0));

END registerN;

ARCHITECTURE rtl_arc OF registerN IS

BEGIN

PROCESS (clk)

BEGIN

IF (clk'event AND clk ='1') THEN

ELSIF (en ='1') THEN

q <= d;

ELSE

q <= q;

END IF;

END PROCESS;

END rtl_arc;

串入/串出移位寄存器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY dff IS

PORT (d : IN std_logic;

clk : IN std_logic;

q : OUT std_logic);

END dff;

ARCHITECTURE rtl OF dff IS

BEGIN

PROCESS (clk)

BEGIN

IF (clk'event AND clk = '1') THEN

q <= d;

END IF;

END PROCESS;

END rtl;

①、

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY shift_reg IS

PORT (d1 : IN std_logic;

cp : IN std_logic;

d0 : OUT std_logic);

END shift_reg;

ARCHITECTURE structure OF shift_reg IS

COMPONENT dff

PORT (d : IN std_logic;

clk : IN std_logic;

q : OUT std_logic);

END COMPONENT;

SIGNAL q : std_logic_vector(4 DOWNTO 0);

BEGIN

q(0) <= d1;

dff1: dff PORT MAP (q(0),cp,q(1));

dff2: dff PORT MAP (q(1),cp,q(2));

dff3: dff PORT MAP (q(2),cp,q(3));

dff4: dff PORT MAP (q(3),cp,q(4));

d0 <= q(4);

END structure;

②、

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY shift_reg IS

PORT (d1 : IN std_logic;

cp : IN std_logic;

d0 : OUT std_logic);

END shift_reg;

ARCHITECTURE structure OF shift_reg IS

COMPONENT dff

PORT (d : IN std_logic;

clk : IN std_logic;

q : OUT std_logic);

END COMPONENT;

SIGNAL q : std_logic_vector(4 DOWNTO 0);

BEGIN

q(0) <= d1;

G1: FOR i IN 0 TO 3 GENERATE

dffx: dff PORT MAP (q(i),cp,q(i+1));

END GENERATE G1;

d0 <= q(4);

END structure;

③、

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY shift_regN IS

GENERIC (n : integer:=4);

PORT (d1 : IN std_logic;

cp : IN std_logic;

d0 : OUT std_logic);

END shift_regN;

ARCHITECTURE structure_arc OF shift_regN IS

COMPONENT dff

PORT (d, clk : IN std_logic;

q : OUT std_logic);

END COMPONENT;

SIGNAL q : std_logic_vector(n-1 DOWNTO 1);

BEGIN

G1:FOR i IN 0 TO n-1 GENERATE

P1:IF (i = 0) GENERATE

dffx: dff PORT MAP (d1,cp,q(i+1));

END GENERATE P1;

P2:IF (i = n-1) GENERATE

dffx: dff PORT MAP (q(i),cp,d0);

END GENERATE P2;

P3:IF ((i /= 0) AND (i /= n-1)) GENERATE

dffx: dff PORT MAP (q(i),cp,q(i+1));

END GENERATE P3;

END GENERATE G1;

END structure_arc;

串入/并出移位寄存器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY dff IS

PORT (d : IN std_logic;

clk : IN std_logic;

q : OUT std_logic);

END dff;

ARCHITECTURE rtl OF dff IS

BEGIN

PROCESS (clk)

BEGIN

IF (clk'event AND clk = '1') THEN

q <= d;

END IF;

END PROCESS;

END rtl;

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY shift_reg IS

PORT (d1 : IN std_logic;

cp : IN std_logic;

q : OUT std_logic_vector(3 DOWNTO 0));

END shift_reg;

ARCHITECTURE structure_arc OF shift_reg IS

COMPONENT dff

PORT (d : IN std_logic;

clk : IN std_logic;

q : OUT std_logic);

END COMPONENT;

SIGNAL q_temp : std_logic_vector(4 DOWNTO 1);

BEGIN

G1:FOR i IN 0 TO 3 GENERATE

P1:IF (i = 0) GENERATE

dffx: dff PORT MAP (d1,cp,q_temp(i+1));

END GENERATE P1;

P2:IF (i /= 0) GENERATE

dffx: dff PORT MAP (q_temp(i),cp,q_temp (i+1));

END GENERATE P2;

END GENERATE G1;

q <= q_temp(4 DOWNTO 1);

END structure_arc;

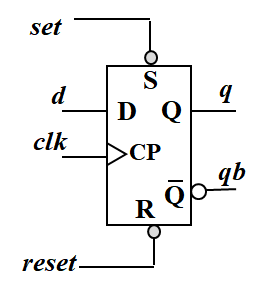

(4)、计数器

四位二进制同步计数器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.std_logic_arith.ALL;

USE IEEE.std_logic_unsigned.ALL;

ENTITY counter IS

PORT (clk, areset, sset ,enable : IN std_logic;

cout : OUT std_logic;

q : BUFFER std_logic_vector(3 DOWNTO 0));

END counter;

ARCHITECTURE rtl_arc OF counter IS

BEGIN

PROCESS (clk,areset)

BEGIN

IF (areset ='1') THEN

q <= '0';

ELSIF (clk'event AND clk ='1') THEN

IF (sset ='1') THEN

q <= "1010";

ELSIF (enable ='1') THEN

q <= q +1;

ELSE

q <= q;

END IF;

END IF;

END PROCESS;

cout <= '1' WHEN q = "1111" AND enable ='1'

ELSE '0';

END rtl_arc;

同步可逆计数器

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.std_logic_arith.ALL;

USE IEEE.std_logic_unsigned.ALL;

ENTITY counterN IS

GENERIC (n : integer:=8);

PORT (clk,areset,sset,enable,updown : IN std_logic;

q : BUFFER std_logic_vector(n-1 DOWNTO 0));

END counterN;

ARCHITECTURE rtl_arc OF counterN IS

BEGIN

PROCESS (clk,areset)

BEGIN

IF (areset ='1') THEN

q <= '0';

ELSIF (clk'event AND clk ='1') THEN

IF (sset ='1') THEN

q <= '1';

ELSIF (enable ='1') THEN

IF (updown ='1') THEN

q <= q +1;

ELSE

q <= q -1;

END IF;

ELSE

q <= q;

END IF;

END IF;

END PROCESS;

END rtl_arc;

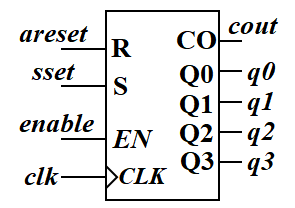

8、有限状态机

①、摩尔型

②、米里型

(1)、描述有限状态机功能的VHDL

①、至少包括一个状态信号,用来指定有限状态机的状态

②、包含状态转移指定和输出指定,对应于控制单元中与每个控制步骤有关的转移条件

③、包含时钟信号,用来同步

④、包含同步或异步复位信号

(2)、设计存储控制器

状态转移图

①、单进程

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY store_controller IS

PORT (ready clk read_write : IN std_logic;

we,re : OUT std_logic);

END store_controller;

ARCHITECTURE state_machine OF store_controller IS

TYPE state_type IS (idle,decision,read,write);

SIGNAL state : state_type;

BEGIN

one_process:PROCESS (clk)

BEGIN

IF (clk'event AND clk ='1') THEN

CASE state IS

WHEN idle => IF (ready ='1') THEN

state <= decision;

ELSE

state <= idle;

END IF;

WHEN decision => IF (read_write ='1') THEN

state <= read;

ELSE

state <= write;

END IF;

WHEN read => IF (ready ='1') THEN

state <= idle;

ELSE

state <= read;

END IF;

WHEN write => IF (ready ='1') THEN

state <= idle;

ELSE

state <= write;

END IF;

END CASE;

END IF;

END PROCESS;

re <= '1' WHEN state = read ELSE '0';

we <= '1' WHEN state = write ELSE '0';

END state_machine;

②、三进程

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY store_controller IS

PORT (ready : IN std_logic;

clk : IN std_logic;

read_write : IN std_logic;

we,oe : OUT std_logic);

END store_controller;

ARCHITECTURE state_machine OF store_controller IS

TYPE state_type IS (idle,decision,read,write);

SIGNAL present_state,next_state : state_type;

BEGIN

nextstate_logic:PROCESS (present_state,ready,read_write)

BEGIN

CASE present_state IS

WHEN idle => IF (ready ='1') THEN

next_state <= decision;

ELSE

next_state <= idle;

END IF;

WHEN decision => IF (read_write ='1') THEN

next_state <= read;

ELSE

next_state <= write;

END IF;

WHEN read => IF (ready ='1') THEN

next_state <= idle;

ELSE

next_state <= read;

END IF;

WHEN write => IF (ready ='1') THEN

next_state <= idle;

ELSE

next_state <= write;

END IF;

END CASE;

END PROCESS;

state_register:PROCESS (clk)

BEGIN

IF (clk'event AND clk ='1') THEN

present_state <= next_state;

END IF;

END PROCESS;

output_logic:PROCESS (present_state)

BEGIN

CASE present_state IS

WHEN idle => we <= '0'; oe <= '0';

WHEN decision => we <= '0'; oe <= '0';

WHEN read => we <= '0'; oe <= '1';

WHEN write => we <= '1'; oe <= '0';

END CASE;

END PROCESS;

END state_machine;